国際特許分類[G06T1/60]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | メモリ管理 (517)

国際特許分類[G06T1/60]に分類される特許

21 - 30 / 517

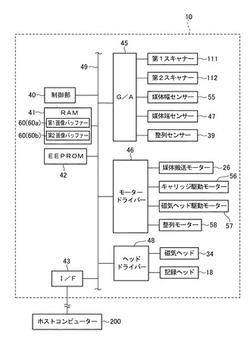

光学読取装置、光学読取装置の制御方法、及び、プログラム

【課題】リングバッファーにおける書き込み可能な領域を多く確保する。

【解決手段】制御部40は、ライトポインターと、リードポインターとの間に介在するラインであって、読み出しを必要としないラインデータが書き込まれているラインについては、当該ラインに書き込まれたラインデータを読み出すことなく、リードポインターを所定方向へ向かって移動させるダミーリード処理を実行する。

(もっと読む)

画像変形装置および命令付加装置

【課題】キャッシュミスのないアクセスを可能にする。

【解決手段】画像変形装置10は、画像を格納するフレームメモリ12と、フレームメモリ12に格納された画像に施す変形処理パラメータP1にプリフェッチ命令P2が付加されたプリフェッチ命令付変形処理パラメータP3を格納するパラメータメモリ13と、フレームメモリ12に格納された画像の画素データの一部を一時的に格納することで、フレームメモリ12からの画素データ読み込み効率を向上させるキャッシュメモリ14と、パラメータメモリ13に格納されたプリフェッチ命令P2に従ってフレームメモリ12からキャッシュメモリ14に画素データをロードするプリフェッチ制御部15と、パラメータメモリ13に格納された変形処理パラメータP1を使用してキャッシュメモリ14に格納された画像に変形処理を施す変形処理部16とを備える。

(もっと読む)

光学読取装置、光学読取装置の制御方法、及び、プログラム

【課題】読み出しが終了していないデータが書き込まれている領域に対して、新たにデータが書き込まれることを効果的に防止する。

【解決手段】制御部40は、リードポインターに追従する破棄ポインターによって、破棄ポインターをライトポインターが所定方向側に超えないように、ライトポインターの移動を制御すると共に、リードポインターの位置にかかわらず、読み出しが完了していないデータを含むラインデータが書き込まれている前記ラインの位置を所定方向側に超えないように、破棄ポインターの移動を制御する。

(もっと読む)

画像形成装置及び方法

【課題】スキューずれ角度がプリントヘッドの取り付け精度により一定の場合に、補正に必要となるラインバッファの容量を削減する。

【解決手段】スキューずれ角度に対応して主走査方向の画像データをスキュー補正対象のブロック数に分割するスキュー画像処理部5と、主走査方向にライン毎に入力される画像データを一時的に保存するラインバッファ2と、分割されたブロック数に基づいてラインバッファ2から出力データを読み出すアドレスを生成するラインバッファリードアドレス制御部3と、出力データを読み出したリードアドレスからその読み出したアドレスへ入力データを書き込むアドレスを生成するラインバッファライトアドレス制御部4とを備え、スキュー画像処理部5はラインバッファ2の一部を用いてスキューずれ角度に応じたアドレス領域内で制御し既に出力として読み出されたデータが格納されていたアドレスに画像データを書き込みスキュー補正を行う。

(もっと読む)

データ処理装置

【課題】分割ブロック毎の処理に必要なデータが、データ転送の切れ目をまたいでいる場合でも、バッファの記憶容量を増大させることなく、各ブロックの処理間のロス時間を低減することができるデータ処理装置を提供する。

【解決手段】予め定められたデータ取得単位毎にデータを取得するデータ取得部と、1つのデータ取得単位よりも少ない記憶容量の複数の分割バッファを具備し、合計の記憶容量が2つのデータ取得単位以上であるバッファ部と、データが有効であるか否かの有効データ情報を出力する有効データ領域判定部と、分割バッファにデータが格納されているか否かの管理情報を出力するバッファ状態管理部と、管理情報に基づいて、少なくとも有効データ情報に示された有効なデータを含む、分割バッファの記憶容量の単位のデータを分割バッファに書き込むデータ書き込み制御部と、管理情報に基づいて有効なデータを読み出すデータ読み出し制御部とを備える。

(もっと読む)

データ形式変換方法、集積装置

【課題】回路規模と性能のトレードオフをより高次元に両立するデータ形式変換方法を提供すること。

【解決手段】処理回数をs、ラインの一方をH、他方をL、HとLの2つの記憶装置を1カラムとしてカラムの端から各カラムの番号をkとし、各記憶装置をH[k],L[k]で表す場合、s回目の処理では、L[s-1]とH[n/2-s]内のデータはカラム方向へ(S1,S3)、L[s]乃至L[n/2-s]及びH[s-1]乃至H[n/2-s-1]内のデータはライン方向へ移動し(S4)、その他の記憶装置はデータ移動を行わず(S5)、L[k]内のデータがライン方向へ移動する場合はL[k-1]へ、カラム方向へ移動する場合はH[k]へ移動し、H[k]内のデータがライン方向へ移動する場合はH[k+1]へ、カラム方向へ移動する場合はL[k]へ移動し、処理数がn/4になるまで前記s回目の処理を繰り返す、ことを特徴とする。

(もっと読む)

画像形成アレイ用ホストインタフェース

【課題】システムプロセッサがアクセスする画像形成データを直接的に受信することのできる画像形成アレイと共に累積可能なインタフェースを提供する。

【解決手段】画像形成アレイ12を有する画像センサとクロックジェネレータ1Aとからデータを受信し、このデータをプロセッサシステム10へ転送するインタフェース13は、画像形成アレイデータを、該クロック信号により決定された速度で記憶するメモリを備える。このメモリにおけるデータの量に応じて、信号ジェネレータが前記プロセッサシステム10へ伝送するための信号を生成し、また、回路が前記プロセッサシステム10により決定された速度で、前記メモリからのデータの転送を制御する。前記メモリは、先入れ先出し(FIFO)バッファ、または、アドレス可能メモリであり、このインタフェース13は、前記画像センサと同一のダイ上に集積される。

(もっと読む)

データ転送制御装置

【課題】データ転送量とメモリ使用量の削減、及び画像処理装置における負荷を軽減してシステム全体の処理スループットの向上を実現できるデータ転送制御装置を提供すること。

【解決手段】データ転送制御装置400は、転送制御部401で受信された画像データを記憶するデータ記憶部402と、設定部200によって設定されたデータ処理の内容に従って、データ記憶部402に記憶された前記画像データに対して演算を施すデータ演算部4032と、データ演算部4032で演算された画像データを転送制御部404に出力するように制御するか、データ記憶部402に帰還させるように制御する内部制御部4033とを備える。データ記憶部402に画像データが帰還された場合、データ演算部4032は、データ記憶部402に帰還された画像データに対してさらに演算を施す。

(もっと読む)

画像形成装置およびその制御方法

【課題】画像形成手段(プロッタ)に不正な画像データが転送されるのを防止する。

【解決手段】出力バッファ(24b)にバッファ容量分の画像データが記憶されたことを通知するバッファフル通知部24eと、出力バッファ(24b)に記憶されている画像データの出力バッファ(32a)への読み出し命令が発生し、且つ、バッファフル通知部24eからの通知があった場合に、出力バッファ(24b)に記憶されている画像データを汎用バスB2を介して取得して出力バッファ(32a)に記憶するリード制御部32dとを備える。

(もっと読む)

画像処理装置及び画像処理システム

【課題】キャッシュメモリの利用効率及び外部メモリへのアクセスレイテンシを改善する。

【解決手段】画像処理装置10は、外部メモリ30及びキャッシュメモリ20に接続される。画像処理装置10は、カウンタ11と、座標計算部12と、タグチェッカ13と、画素参照部15と、画素値計算部16と、出力部17と、を備える。カウンタ11は、所定の実行順に従って変換後座標を決定する。座標計算部12は、変換後座標に位置する変換後画素の変換後画素値を計算するための変換前座標を計算する。タグチェッカ13は、変換前画素を参照して変換後画素値を計算することを要求する変換要求を生成する。画素参照部15は、変換要求に基づいて、変換前座標に位置する変換前画素がキャッシュメモリ20に記憶されている場合に、変換前画素をキャッシュメモリ20から読み出す。画素値計算部16は、読み出された変換前画素を参照して、変換後画素値を計算する。出力部17は、変換後画素を外部メモリ30に書き込む。

(もっと読む)

21 - 30 / 517

[ Back to top ]