国際特許分類[G06T1/60]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | メモリ管理 (517)

国際特許分類[G06T1/60]に分類される特許

81 - 90 / 517

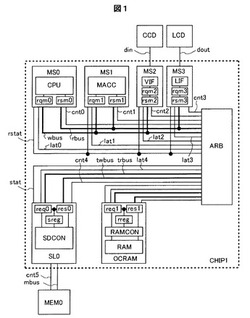

情報処理システム

【課題】メモリ装置をアクセスする複数のマスタに対して、必要なデータを円滑に転送する。

【解決手段】情報処理システムは、メモリ装置(MEM0)と、上記メモリの動作を制御可能なメモリ制御装置(SL0)と、それぞれ上記メモリ制御装置を介して上記メモリ装置へアクセス可能な複数のバスマスタ(MS0〜MS3)とを含む。上記メモリ制御装置は、上記バスマスタからのアクセス要求を保持可能なバッファを含み、上記バッファの利用権を上記バスマスタ毎に設定可能である。

(もっと読む)

画像処理装置および画像処理方法

【課題】画像メモリのアクセス回数を削減することができる画像処理装置および画像処理方法を提供する。

【解決手段】

画像処理部10に搭載されていた画像データ処理部33を画像メモリコントローラ30に搭載させ、併せてアドレス変換部32、制御部31を搭載する構成とする。また、画像メモリ20の仮想読み出しアドレスエリアを定義することによって、メモリ使用量を減らし、メモリアクセス回数を減らすことができ、通信速度の向上を図る。

(もっと読む)

画像処理装置、画像処理方法、コンピュータプログラム

【課題】 入力画像に対して複数種類の画像処理を行う場合、それぞれの画像処理に適した画像を生成するのが望ましい。しかしながら、それらの画像を同時に保持しようとすると、多くのメモリが必要になってしまう。

【解決手段】 本発明では、入力画像に対して複数種類の画像処理(領域解析処理、文字部ベクトル化処理、図画部ベクトル化処理など)を行う場合、各画像処理を実行する前にそれぞれの画像処理に適した画像を生成する。そして、画像処理の処理結果は領域情報に格納するとともに、各画像処理で使用したワークメモリを開放してから、次の画像処理を行う。

(もっと読む)

画像処理装置及び画像撮像装置

【課題】安価なメモリ(フレームメモリ)でも原画像の自由な変形や歪補正等を行い、高画質な映像を容易に得られる画像処理装置を提供する。

【解決手段】メモリ220から画像データを読み出す際に座標変換により、画像の変形を反映した読出しアドレスを計算する手段230、入力された画像データをメモリ220に書込み、読出しアドレスに基づいてメモリ220から画像データを読み出す手段210、メモリ220から読み出される画像データの主走査方向の画素数を、出力画面の主走査方向の画素数に対して小さくなるように制限する手段212、出力画面の主走査方向の画素数に対して主走査方向の画素数が小さくメモリ220から読み出された画像データを、出力画面の主走査方向の画素数となるように伸張する手段240を備える。

(もっと読む)

画像処理装置および画像形成装置

【課題】 小さいサイズのバッファメモリを使用し少ないメモリアクセスで、カラースキャンにより得られた画像データをブロックごとに処理する。

【解決手段】 ラスタ書込部12は、複数色のラインデータをそれぞれ、ラインセンサ1R,1G,1Bの間隔に対応するオフセット分だけアドレスをシフトさせて、バッファメモリ3に副走査方向に沿って順番に書き込む。そして、ブロック読出部13は、バッファメモリ3に書き込まれた各色についての複数のラインデータからブロックデータ31R,31G,31Bを読み出し、ブロック画像処理部14は、そのブロックデータ31R,31G,31Bに対して所定のデータ処理を行う。

(もっと読む)

汎用使用のための処理ユニット内部メモリ

【解決手段】

汎用使用のための内部メモリを有するグラフィクス処理ユニット(GPU)及びそのアプリケーションがここに開示される。そのようなGPUは、第1の内部メモリと、第1の内部メモリに結合される実行ユニットと、第1の内部メモリを他の処理ユニットの第2の内部メモリに結合するように構成されるインタフェースと、を含む。第1の内部メモリは積層ダイナミックランダムアクセスメモリ(DRAM)又は埋め込みDRAMを備えていてよい。インタフェースは第1の内部メモリをディスプレイデバイスに結合するように更に構成されていてよい。GPUは第1の内部メモリを中央処理ユニットに結合するように構成される別のインタフェースを含んでいてもよい。またGPUはソフトウエアにおいて具現化され且つ/又はコンピューティングシステム内に含まれていてよい。

(もっと読む)

画像読取装置および画像処理方法

【課題】パラレル入力された画像データの並び替えによる、回路規模の増大やコストの上昇を、なるべく抑えるための技術を提供する。

【解決手段】複数チャンネルを有するラインイメージセンサーを備える画像読取装置であって、少なくとも1ライン分の画像データを格納する記憶部と、複数チャンネルのそれぞれから並列に出力される画像データに対する所定の画像処理を並列に行って出力する画像処理部と、画像処理部の後段に設けられ、画像処理部から並列に出力される画像データのそれぞれをラインイメージセンサーにおける複数のチャンネルの並び順となるように、画像データを記憶部に書き込む、並び替え処理部と、を有する。

(もっと読む)

メモリコントローラ、画像処理システムおよびメモリアクセスの制御方法

【課題】 画像データを読み書きする半導体メモリのアクセス効率を向上する。

【解決手段】 アクセスコスト計算部は、読み出しアクセスおよび書き込みアクセスの少なくともいずれかに必要なサイクル数をアクセスコストとして複数のメモリマップ毎に計算する。メモリマップ選択部は、メモリマップの中からアクセスコストが最も低いメモリマップを選択する。パラメータ変換部は、メモリマップ選択部が選択したメモリマップに基づいて、アクセスアドレスを変換する。アクセス制御部は、変換されたアクセスアドレスに基づいて半導体メモリにアクセスするための制御信号を生成する。アクセスコストの低いメモリマップを用いて半導体メモリにアクセスすることで、半導体メモリのアクセス効率を向上できる。

(もっと読む)

画像処理装置

【課題】配線数の増大を抑え、回路規模や信号伝達遅延時間の増加を防止して、画像データを90度単位で回転する画像処理装置を提供する。

【解決手段】連続する所定数の画素データ単位で画像データを分割した各画素群の画素データのそれぞれを入力して記憶する複数のメモリ1〜4と、画像データの回転を指示する指示情報を生成する動作モード制御部7と、指示情報に応じて、複数のメモリ1〜4のそれぞれから画素データを読み出すアドレスを複数のメモリのそれぞれに出力して、前記複数のメモリの各対応するアドレスに記憶された画素データを読み出すコントローラ部5と、複数のメモリ1〜4から読み出した複数の画素データを指示情報に応じて並び替えて出力するセレクタ部6とを有する。

(もっと読む)

画像処理装置

【課題】 画像処理装置において、符号化後のバンドデータを構成するすべてのデータの格納場所のアドレスが連続となるようにして、符号化後のバンドデータの書き込みおよび読み出しにおける遅延の発生を抑制する。

【解決手段】 画像データを構成する複数のバンドデータに対して順番に画像処理を行う画像処理装置において、RAM14は、固定長のバッファ領域を有し、JPEG符号化回路12は、複数のバンドデータを順番に可変長符号化していき、符号化後のバンドデータをバッファ領域の先頭から順番に書き込んでいき、符号化後のバンドデータの終端が、バッファ領域の終端部分における所定長の境界領域内に位置する場合には、次の符号化後のバンドデータをバッファ領域の先頭から書き込む。

(もっと読む)

81 - 90 / 517

[ Back to top ]