国際特許分類[G11C13/00]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 11/00,23/00,または25/00に包含されない記憶素子の使用によって特徴づけられたデジタル記憶装置 (1,014)

国際特許分類[G11C13/00]の下位に属する分類

化学変化に基づく素子を用いるもの (16)

光学的素子を用いるもの (45)

国際特許分類[G11C13/00]に分類される特許

1 - 10 / 953

記憶装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

スイッチ素子を有するメモリシステム

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体記憶装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

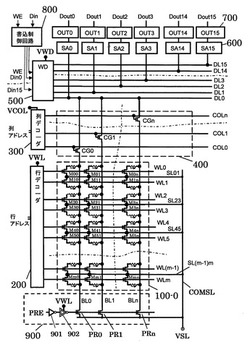

抵抗変化型不揮発性メモリ

【課題】抵抗変化型不揮発性メモリのメモリセルの面積を縮小し、かつ、消費電力を少なくする。

【解決手段】行選択線をゲート端子に接続したメモリセル選択用トランジスタと抵抗変化型素子を直列に接続した回路のメモリセルの端子をビット線とソース線とに接続した抵抗変化型不揮発性メモリの前記ソース線を前記行選択線に平行に配線し、前記ビット線を前記行選択線に直交させて配線し、前記ソース線に一定値のソース電圧を加えて前記メモリセルへのデータの書き込み及び読出しを行い、前記ビット線に、前記ソース電圧より高い電圧と低い電圧とを切り替えて加えることで異なる値のデータを前記メモリセルへ書き込む。

(もっと読む)

半導体記憶装置

【課題】データの誤読み出しを防止することが出来る半導体記憶装置を提供すること。

【解決手段】データを保持可能なメモリセルMCが行及び列に沿って設けられ、前記データの読み出し単位とされるブロックが第1方向に沿って複数形成されたストライプSTPと、前記ブロックが形成された直下に各々が設けられ、前記データを読み出すセンスアンプSAと、前記第1方向に沿って前記ストライプを貫通するように形成され、前記ブロックから読み出された前記データを前記センスアンプSAに転送するグローバル信号線と、前記センスアンプが配置された各々のエリアと複数の前記ブロックのうち前記データの読み出し対象とされた前記ブロックとの位置関係に応じて各々の前記センスアンプに流すリファレンス電流の値を制御する制御部とを具備する。

(もっと読む)

半導体メモリ装置、このためのセットプログラム制御回路及びプログラム方法

【課題】消去命令に応答してセットデータをプログラムできる半導体メモリ装置と、このためのセットプログラム制御回路及びプログラム方法を提供する。

【解決手段】本発明に係る半導体メモリ装置は、プログラミングイネーブル信号に応答して第1書き込み制御信号、第2書き込み制御信号及びプログラム完了信号を生成するプログラムパルス生成部と、消去命令及びプログラム完了信号に応答してセットプログラミングイネーブル信号を指定された回数だけ反復生成するセットプログラム制御回路と、消去命令に応答して第1書き込み制御信号をディスエーブルし、セットプログラミングイネーブル信号に応答してプログラミングイネーブル信号を生成するコントローラとを含むことができる。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の配線での電圧降下の緩和を図る。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と、半導体基板上に3次元配列された複数のメモリセルと、前記メモリセルを介在させて三層以上積層された複数の配線と、制御回路と、を備えている。前記制御回路は、前記複数のメモリセルの中から選択された選択セルを半導体基板に対して垂直方向に挟む一対の配線間に電位差を与えて前記選択セルに状態を変化させる電流を流し、且つ前記選択セルとは異なる層で前記選択セルと共有された配線に接続された非選択セルを挟む一対の配線間にも電位差を与えて、前記非選択セルに、前記選択セルに流れる電流よりも小さな電流を前記選択セルに流れる電流と同じ方向に流す。

(もっと読む)

半導体記憶装置

【課題】不揮発性メモリ部内蔵のSRAMの特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1とビット線BLとの間に抵抗変化層Rを有するReRAM部RM1を設け、アクセストランジスタAcc2とビット線/BLとの間に抵抗変化層Rを有するReRAM部RM2を設ける。SRAM通常動作期間の終了時において、例えば、蓄積ノードAに低電位(L=0V)、蓄積ノードBに高電位(H=1.5V)が保持されている場合、ReRAM部RM1をオン状態(ON)とし、ReRAM部RM2をオフ状態(OFF)とすることで、SRAMの保持データをReRAM部へ書き込み、再び、SRAM通常動作となった場合には、蓄積ノードAおよびBに対応するデータ書き戻すとともに、ReRAM部RM1、RM2の双方をオン状態に(リセット)する。

(もっと読む)

相変化メモリ・セルをプログラミングするための方法、コンピュータ・プログラム、および装置、ならびに相変化メモリ・デバイス(相変化メモリ・セルのプログラミング)

【課題】s>2通りのプログラム可能セル状態を有する相変化メモリ・セルをプログラミングするための方法および装置を提供する。

【解決手段】少なくとも1つの制御信号VBLを印加して、セルをプログラミングするためのプログラミング・パルスを発生する。プログラミング・パルス中に少なくとも1つの前記制御信号VBLを変更して、プログラミングすべきセル状態に依存してプログラミング・パルスを整形し、前記セル状態をプログラミングするためのそれぞれのプログラミング軌道に対応する複数のプログラミング・パルス波形(波形A〜D)のうちの選択された1つを発生する。選択されたプログラミング・パルス波形は、プログラミングすべきセル状態を含むプログラミング軌道に対応する。

(もっと読む)

1 - 10 / 953

[ Back to top ]