国際特許分類[G11C14/00]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 電源遮断時にバックアップするための,揮発性メモリセルと不揮発性メモリセルの配置によって特徴づけられたデジタル記憶装置 (45)

国際特許分類[G11C14/00]に分類される特許

1 - 10 / 45

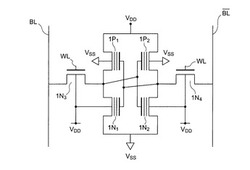

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

記憶装置及び半導体装置

【課題】消費電力を抑えることができる記憶装置を提供する。

【解決手段】第1クロック信号に従って、データを含む信号の電位の極性を反転させることで、出力電位を生成する第1論理素子と、第1論理素子が生成する出力電位を保持する第2論理素子及び第3論理素子と、トランジスタを用いたスイッチング素子と、第2論理素子及び第3論理素子において保持される第1論理素子の出力電位が、スイッチング素子を介して与えられることで、データを記憶する容量素子と、を有し、第2論理素子は、第1クロック信号とは異なる系統の第2クロック信号に従って、第3論理素子の出力電位の極性を反転させることで、第2論理素子の出力電位を生成し、第3論理素子は、第2論理素子の出力電位の極性を反転させることで、第3論理素子の出力電位を生成する記憶装置。

(もっと読む)

キャッシュメモリ、及びキャッシュメモリの駆動方法

【課題】低消費電力動作が可能で、且つキャッシュヒット率が向上したキャッシュメモリと、その駆動方法を提供する。

【解決手段】キャッシュメモリが有するメモリセット内の1つのメモリセルに2つのデータ格納部(第1格納部、第2格納部)と、1つのデータ転送部を設ける構成とし、2つのデータ格納部間でデータ転送部を介してそれぞれのデータを移行できる構成とする。さらに、2つのデータ格納部のうち、いずれか1つのデータ格納部は、外部から入力されるデータを格納可能で、且つメモリセットに対に設けられる比較回路にデータを出力可能な構成とすればよい。

(もっと読む)

記憶装置、記憶装置の駆動方法

【課題】書き込み速度を損なうことなく、消費電力の低減された記憶装置を提供する。

【解決手段】書き込み信号に応じて、第1のノードに電源電位を入力するか、電位を保持させるか、接地させるかを選択するコントローラと、一方の電極が前記第1のノードに接続する第1の容量素子と、第1の容量素子の他方の電極に、書き込み信号を遅延して出力する遅延回路と、第1のノードと接続されるゲート電極と、入力データ信号が入力される第1の電極と、入力データ信号を記憶する第2のノードと接続される第2の電極とを備える第1のトランジスタと、第2のノードと接続され、読み出し信号に応じて第2のノードの電位に応じた信号を出力する読み出し回路と、を有し、第2のノードは、一方の電極が接地された第2の容量素子の他方の電極と、読み出し回路が備える第2のトランジスタのゲート電極と、が接続される記憶装置を提供すること。

(もっと読む)

半導体装置

【課題】所望のタイミングでデータの評価、書き換えを行うことができる半導体装置を提供する。

【解決手段】フリップフロップ回路と、選択回路と、選択回路を介して前記フリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含むレジスタ回路と、ビット線と、データ線と、を有し、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、データ線の電位またはビット線の電位に応じたデータを選択的に不揮発性記憶回路に格納する半導体装置。

(もっと読む)

記憶回路、信号処理回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】酸化物半導体を用いて形成されたトランジスタと、該トランジスタのソース電極またはドレイン電極の一方と接続された容量素子を用いて、不揮発性の記憶回路を構成する。記憶回路に予めハイレベル電位を書き込んでおき、退避させるデータがハイレベル電位の場合は、そのままの状態を維持し、退避させるデータがローレベル電位の場合は、ローレベル電位を記憶回路に書き込むことで、書き込み速度を向上させた信号処理回路を実現できる。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

記憶素子、信号処理回路

【課題】新たな構成の不揮発性の記憶素子、それを用いた信号処理回路を提供する。

【解決手段】第1の回路と第2の回路とを有し、第1の回路は第1のトランジスタと第2のトランジスタとを有し、第2の回路は第3のトランジスタと第4のトランジスタとを有する。第1の信号に対応する信号電位は、オン状態とした第1のトランジスタを介して第2のトランジスタのゲートに入力され、第2の信号に対応する信号電位は、オン状態とした第3のトランジスタを介して第4のトランジスタのゲートに入力される。その後、第1のトランジスタ及び第3のトランジスタをオフ状態とする。第2のトランジスタの状態と第4のトランジスタの状態との両方を用いて、第1の信号を読み出す。第1のトランジスタ及び第3のトランジスタは、チャネルが酸化物半導体層に形成されるトランジスタとする。

(もっと読む)

信号処理装置

【課題】消費電力を抑えることができる信号処理装置を提供する。

【解決手段】信号処理装置が有する記憶回路に、酸化物半導体にチャネルが形成されるトランジスタを適用することで、電力の供給を停止している間もデータの保持(記憶)を可能とする。記憶回路に記憶されているデータは、信号処理装置への電力の供給を停止している間も、破壊すること無く読み出すことができる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

1 - 10 / 45

[ Back to top ]