国際特許分類[G11C15/04]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 1つ以上の特徴表示部分を含む情報が書き込まれ,情報の読出しはそれらの1つ以上の特徴表示部分について探索することによって行なわれるデジタル記憶装置,すなわち連想記憶または内容アドレス記憶装置 (108) | 半導体素子を用いるもの (101)

国際特許分類[G11C15/04]に分類される特許

1 - 10 / 101

連想メモリ

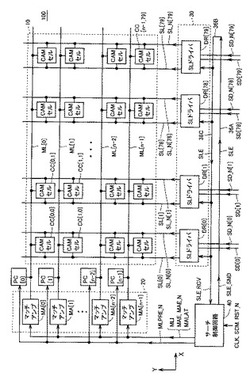

【課題】従来よりも高周波数動作が可能な連想メモリを提供する。

【解決手段】サーチ線ドライバDRは、サーチ制御回路40から供給されたサーチ線イネーブル信号SLEが活性化したとき、CAMメモリアレイ10の各CAMセルにサーチ線対SL,SL_Nを介して検索データSD,SD_Nを転送する。サーチ線イネーブル信号SLEは、サーチ制御回路40に接続された1本の制御信号線36(36A,36B,36C)を介して各サーチ線ドライバDRに伝送される。制御信号線36は、サーチ線イネーブル信号SLEが、マッチアンプMAから見て遠い側からサーチ線ドライバDRの配列順で各サーチ線ドライバDRと制御信号線との接続ノードを通過するように、各サーチ線ドライバDRと接続される。

(もっと読む)

連想メモリ

【課題】誤検索を抑制可能な連想メモリを提供する。

【解決手段】連想メモリは、R個の距離/時間変換回路DT1〜DTRを備える。R個の距離/時間変換回路DT1〜DTRの各々は、NAND回路40と、Nビットステージ41〜4kとを含む。Nビットステージ41〜4kは、それぞれ、参照データと検索データとの間の距離が大きいほど、より長い遅延時間によってNAND回路40からの信号を遅延して発振信号を発振し、参照データと検索データとの間の距離が小さいほど、より短い遅延時間によってNAND回路40からの信号を遅延して発振信号を発振する。そして、距離/時間変換回路DT1〜DTRから出力されたR個の発振信号のうち、最も早く変化する発振信号がWinner行の発振信号として検出される。

(もっと読む)

半導体記憶装置

【課題】 効率的なデータ検索が可能な半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、複数の単位構造を含む。単位構造は、メモリセルとそれぞれ接続されたセンスアンプ(SA)と、センスアンプと接続された第1線(LBUS)と、第1線と接続された第1ラッチ(XDL)と、第1線と接続された第2ラッチ(LDL)と、第1線と接続され、第1および第2ラッチ中のデータに対する論理演算を行なう演算回路(Y)と、を含む。複数の第1検知回路(31,32)は、各々が複数の単位構造の相違する一部を含んだ複数の単位構造群とそれぞれ接続され、対応する単位構造群において少なくとも1つの第1線の電位がLレベルであることを検知する。第2検知回路(43)は、少なくとも1つの第1検知回路によって検知がなされたことを検知する。

(もっと読む)

連想メモリ内の電力消費を減少させるための方法と装置

【課題】マルチ−レベルの階層的連想メモリ(CAM)回路内の電力消費を性能に悪影響を与えること無しに低減する。

【解決手段】CAM回路は複数の低レベルマッチライン、複数の高レベルマッチラインおよびマッチライン回復回路を含む。低レベルマッチラインは前評価期間中は前評価状態に戻されるように構成される。高レベルマッチラインは評価期間中は1つまたはそれ以上の低レベルマッチラインのそれぞれのグループの評価状態を獲得するように、そして前評価期間中は前評価状態に戻される様に構成される。マッチライン回復回路は少なくとも1つの低レベルマッチラインが対応するイネーブル情報、例えば、マッチラインサーチ結果が使用されるべきかどうかを示す1つまたはそれ以上のビットに反応して前評価状態に戻されるのを防ぐように構成される。

(もっと読む)

内容参照メモリ

【課題】未使用の記憶領域の発生を低減することができる内容参照メモリを提供する。

【解決手段】メモリアレイ2は、複数のバンク1〜Nを含み、検索対象のIPアドレスを格納する。メモリアレイ2は、可変数のバンクからなる複数のブロックを含む。同一のブロックのバンクにはプリフィックスが同一のIPアドレスが格納される。プリサーチ回路5は、IPアドレスを検索データとして受けて、検索データと同一のIPアドレスがいずれのブロックに格納されているかをプリサーチする。検索判定部14は、プリサーチによって特定されたブロックから読み出されたIPアドレスと検索データとを比較する。

(もっと読む)

連想メモリ更新のためのシステム

【課題】連想メモリを更新する際の再構築に要する時間及び労力の増大を解消する。

【解決手段】システムは連想メモリ、第1テーブル、第2テーブル、コンパレータ、及びアップデータを含む。連想メモリはデータ及びデータ間の連想を含み、第1テーブルから構築する。第1テーブルは、第1及び第2フィールドを伴うレコードを含む。連想メモリは第1フィールドを取り込み、第2フィールドの取り込みを回避するように構成する。第2テーブルは、第1フィールドが連想メモリによって取り込み済みかどうか、又は連想メモリによって忘却処理済みかどうかを示す情報を保存する。コンパレータは、第1フィールドを連想メモリによって忘却処理すべきかどうか、又は取り込むべきかどうかを特定するため、第1テーブルと第2テーブルの比較を行う。アップデータは、第1フィールドの取り込み又は忘却処理のいずれか一つを実施することによって、連想メモリを更新する。

(もっと読む)

半導体記憶装置、情報処理装置

【課題】処理量が少ないデータ転送が可能なメモリシステムを提供する。

【解決手段】半導体記憶装置は、メモリ(14)と、制御部(12, 13)を含む。メモリは、データと、データを特定するための検索キーとデータが格納されている実アドレスと対応付けたエントリを複数含む検索情報と、を保持する。制御部は、第1コマンドを受け取ると、第1コマンドが検索キーを特定する場合はこの検索キーを含むエントリに対応するデータを出力し、第1コマンドが実アドレスを特定する場合はこの実アドレスを含むエントリに対応するデータを出力する。

(もっと読む)

半導体記憶装置および半導体記憶装置の駆動方法

【課題】外部に設けられた低速な記憶装置へのアクセス頻度が低減され、処理速度が速く、消費電力が低減された半導体記憶装置を提供する。または、外部に設けられた低速な記憶装置へのアクセス頻度が低減された処理速度が速く、消費電力が低減された半導体記憶装置の駆動方法を提供する。

【解決手段】あらかじめアドレスの第1のビット列のいずれかが割り当てられたラインをk(kは2以上の自然数)行備えるアレイがj(jは2以上の自然数)個設けられたセットをi(iは自然数)個備える記憶部と、比較回路と、選択回路と、制御回路を用いて半導体記憶装置を構成する。また、目的とするアドレスの第1のビット列があらかじめ割り当てられたi×j行のラインを、制御回路と、選択回路のキャッシュヒット若しくはキャッシュミスの判定とを用いて1回以上j回以下検索することにより、目的とするデータが格納されているラインを特定する。

(もっと読む)

記憶装置

【課題】回路面積を小さくする。

【解決手段】記憶された第1のデータと検索データである第2のデータを照合することにより、第1のデータの内容を判別する機能を有するメモリセルを具備し、メモリセルは、オン状態又はオフ状態になることにより第1のデータの書き込み及び保持を制御する第1のトランジスタと、ソース及びドレインの一方の電位が第2のデータであり、ゲートの電位が第1のデータとなる第2のトランジスタと、第2のトランジスタと逆の導電型であり、ソース及びドレインの一方が第2のトランジスタのソース及びドレインの他方に電気的に接続され、ゲートの電位が第1のデータとなる第3のトランジスタと、を備える。

(もっと読む)

仮想接地を制御してCAMRAMを分割するための回路とその方法

【課題】CAMRAMバンクを仮想接地により分割する方法を提供する。

【解決手段】CAMバンクが、CAMドライバ回路を対応数だけ用意することなく、サブバンクを有する入力内の放電回路を選択的に活性化することにより、2個又はそれ以上のサブバンクに機能的に分割される。少なくとも1個の選択的に活性化されるスイッチング回路がサブバンクの放電回路内の各放電コンパレータの仮想接地ノードと回路接地との間に挿入される。スイッチング回路が非導通状態のときは、仮想接地ノードは回路接地より充分に高い電圧レベルに維持されてCAMアクセス時間内に接続された整合ラインの放電を防止する。スイッチング回路が導通状態のときは、仮想接地ノードは回路接地に低下し、接続された整合ラインはコンパレータの非整合動作により放電される。アドレスビットから復号化により形成された制御信号がスイッチング回路に分配され、CAMサブバンクが選択される。

(もっと読む)

1 - 10 / 101

[ Back to top ]