国際特許分類[G11C17/00]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 一度だけプログラム可能なリードオンリメモリ;半永久的記憶装置,例.手でリプレースできる情報カード (379)

国際特許分類[G11C17/00]の下位に属する分類

磁気的または誘導的素子を用いるもの

容量的素子を用いるもの (6)

ダイオード素子を用いるもの (43)

半導体装置を用いるもの,例.バイポーラ素子を用いるもの (48)

その記憶内容が,結合素子の状態を永久に変えることによって連結リンクを選択的に設定,切断または変更することにより決められるもの,例.PROM (188)

国際特許分類[G11C17/00]に分類される特許

1 - 10 / 94

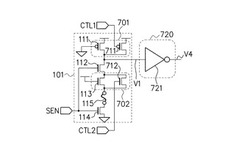

ヒューズ素子読み出し回路

【課題】十分な読み出しマージンを確保し、ヒューズ素子のデータ読み出しの際に誤判定を防止することができるヒューズ素子読み出し回路を提供することを課題とする。

【解決手段】切断済みと未切断とで抵抗値が異なる第1のヒューズ素子(115)と、通常モードと試験モードとで異なる抵抗値を有する第1の抵抗回路(701,702)と、前記第1のヒューズ素子の抵抗値及び前記第1の抵抗回路の抵抗値に応じた読み出し電圧を出力する読み出し電圧出力回路(101)とを有することを特徴とするヒューズ素子読み出し回路が提供される。

(もっと読む)

半導体ディスク寿命監視装置

【課題】不揮発性の半導体ディスクの寿命を監視する半導体ディスク寿命監視装置を提供する。

【解決手段】半導体ディスク5−1〜5−Kの書込み制御を行うファイルシステム3と、当該ファイルシステム3と前記半導体ディスク5−1〜5−Kを接続するインタフェースドライバ4を備え、当該インタフェースドライバ4により書込みが行われる半導体ディスク5−1〜5−Kの寿命を予測する半導体ディスク寿命監視装置1であって、前記ファイルシステム3からの書込みを書込情報として測定する測定部7と、前記測定結果を累積し第1の保存データ32として保存する保存部8と、前記保存した累積書込情報に基づいて、半導体ディスク5−1〜5−Kの寿命を予測する。

(もっと読む)

半導体記憶装置

【課題】製造ばらつきにより生じる不良ブロックを判定可能な半導体記憶装置を提供する。

【解決手段】メモリセルと、複数の前記メモリセルを含むページ、複数の前記ページを含むブロックを有するメモリセルアレイと、前記ページのうち、第1カラムに対応する第1メモリセルにデータを書き込むとき、プログラム動作を繰り返した第1回数を保持する第1記憶部63と、前記ページのうち、前記第1カラムとは異なる第2カラムに対応する第2メモリセルにデータを書き込むとき、プログラム動作を繰り返した第2回数を保持する第2記憶部64と、第1回数と第2回数の差が規定値を超えたとき、前記第1メモリセルと前記第2メモリセルとを含むブロックを不良ブロックとして登録する制御部6とを備える。

(もっと読む)

半導体記憶装置及びその試験方法

【課題】ローデコーダ側に配置される転送トランジスタの特性評価を実施する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、切り替え部、第一の転送トランジスタ、第一のトランジスタ、及び第二のトランジスタが設けられる。切り替え部が第一の状態のときに第一及び第二のトランジスタがオフし、第一の転送トランジスタがオンし、切り替え部が第二の状態のとき第一及び第二のトランジスタがオンする。

(もっと読む)

プログラム書込システム

【課題】バッテリ電圧が異なる車両の制御対象機器を制御するための、同じハードウエア構成を備えた電子制御装置に対して、正しい制御プログラム以外の書き込みを防止すること。

【解決手段】ECU104が、書込装置101から制御プログラムの提供を受けたときに、検出されたバッテリ電圧VVと、制御プログラム内の使用電圧情報110から取得した使用電圧VSとに基づき、制御プログラムの正誤を判定する。そして、正しい制御プログラムではないと判定した場合、制御プログラムのフラッシュROMへの書込処理を中止する。

(もっと読む)

光パターン表示媒体、光パターン算出方法及び光認証システム

【課題】本発明は、ランダムに配置された個々の発光材料の振動ダイポールモーメントの向き・強度に応じた近接場光からなる光パターンを表示可能な光パターン表示媒体、その光パターンを瞬時に観測可能な光パターン算出方法及び光認証システムを提供することを課題とする。

【解決手段】側面に官能基が取り付けられた炭素繊維材料にクマリン又はその誘導体からなる発光材料を分散させてなる板状部材22と、板状部材22の一面22aに配置された第1の導電部材24と、板状部材22の他面22bに配置された第2の導電部材21とを有し、第1の導電部材24は複数の光透過部23cが互いに等間隔となるように配置された金属基板23であり、光透過部23cの最大径dが前記発光材料の最大発光ピーク波長の1/2以下である光パターン表示媒体10を用いることによって、前記課題を解決できる。

(もっと読む)

半導体装置

【課題】データ書き替えの繰り返しによってメモリセルの閾値電圧が下がりくくなることを防止する。

【解決手段】半導体装置1の各メモリセルMCは、共通の浮遊ゲートFGを有する第1のトランジスタ(読出用)TRAと第2のトランジスタ(書込用)とを含む。制御回路11は、一方のトランジスタに通電したときにメモリセルに流れる電流と、両方のトランジスタに通電したときにメモリセルに流れる電流とを比較することによって、第1および第2のトランジスタにそれぞれ接続されるサブビット線SBL_R,SBL_P間のショートを検出する。

(もっと読む)

不揮発性メモリ装置及びメモリコントローラとこれらの動作方法、メモリシステムの動作方法、並びにウェアレベリング方法

【課題】メモリセルの劣化度を正確に検出することができる不揮発性メモリ装置及びメモリコントローラとこれらの動作方法、メモリシステムの動作方法、並びにウェアレベリング方法を提供する。

【解決手段】本発明の不揮発性メモリ装置の動作方法は、コントローラから出力されたブロックアドレスとイレース命令とを受信する段階と、ブロックアドレスに相応するブロックに対して、イレース命令によって行われるイレース動作が完了するまで、イレース動作に関連したパラメータ値を変更する段階と、最後に変更されたパラメータ値に相応する情報を保存する段階と、コントローラから出力された命令によって、情報をコントローラに伝送する段階と、を有する。

(もっと読む)

書き込み制御回路及び半導体装置

【課題】電気的に1回限りの書き込みが行われる記憶素子への誤書き込みを抑制する。

【解決手段】書き込み制御部11は、電気的に1回限りの書き込みが行われる記憶素子(電気ヒューズ素子2)への書き込みを、書き込みを指示する書き込み信号に応じて制御し、電圧検出部12は、電源電圧、または電気ヒューズ素子2へ供給される書き込み電圧の立ち上がり時に、一定期間、書き込み信号に係わらず電気ヒューズ素子2への書き込みを書き込み制御部11に停止させる。

(もっと読む)

負バイアス温度不安定性に耐性のあるラッチングセンスアンプを有するメモリおよび関連する方法

【課題】OTPメモリセルのための負バイアス温度不安定性(NBTI)耐性の高いラッチングセンスアンプを提供する。

【解決手段】集積回路は、OTPメモリセルと、第1および第2ビット線を介してメモリセルに接続されたセンスアンプ20とを備える。センスアンプは、ラッチを提供するために交差結合第1および第2インバータを備える。第1インバータは、第1ビット線に亘ってメモリセルによって提供された第1データ信号に応答する。第2インバータは、第2ビット線に亘ってメモリセルによって提供された第2データ信号に応答する。第1NBTI補償トランジスタ38は、ソース電極、ドレイン電極、および第1データ信号に応答する第1論理に接続されたゲート電極を備える。第2NBTI補償トランジスタ40は、ソース電極、ドレイン電極、および第2データ信号に応答する第2論理に接続されたゲート電極を備える。

(もっと読む)

1 - 10 / 94

[ Back to top ]