国際特許分類[G11C19/00]の内容

国際特許分類[G11C19/00]の下位に属する分類

磁気素子を用いるもの (1)

共振回路中の非線型誘導素子を用いるもの

能動素子,例.放電管,半導体素子,と結合した磁気素子を用いるもの (1)

ステージの主素子としてキャパシタを用いるもの

放電管を用いるもの

半導体素子を用いるもの (202)

オプト―エレクトロニクス装置,すなわち電気的または光学的に結合された光放射および光―電気装置を用いるもの

超電導素子を用いるもの

3以上の異なる安定状態を有する記憶素子を用いるもの,例.電圧によるもの,電流によるもの,位相によるもの,周波数によるもの

二次元の,例.水平方向と垂直方向に情報が移動するシフト・レジスター

国際特許分類[G11C19/00]に分類される特許

61 - 70 / 283

シフトレジスタ回路

【課題】エンドパルスの入力が不要な双方向シフトレジスタを提供する。

【解決手段】双方向単位シフトレジスタの各段は、クロック端子CKと出力端子OUTとの間のトランジスタQ1と、出力端子OUTを放電するトランジスタQ2と、トランジスタQ1のゲートノードである第1ノードに対し互いに相補な第1および第2電圧信号Vn、Vrをそれぞれ供給するトランジスタQ3,Q4とを備える。最前段の単位シフトレジスタSR1は、第1ダミーシフトレジスタSRD1の出力信号D1に応じてトランジスタQ1のゲートを放電するトランジスタQ3Dを備え、最後段の単位シフトレジスタSRnは、第2ダミーシフトレジスタSRD2の出力信号D2に応じてトランジスタQ1のゲートを放電するトランジスタQ3Dを備える。

(もっと読む)

シフトレジスタ、走査線駆動回路、電気光学装置および電子機器

【課題】トランジスタの劣化を抑制することにより、長寿命化を図ることが可能なシフトレジスタを提供する。

【解決手段】この発明のシフトレジスタは、複数段のシフトレジスタ単位回路14を備える。また、複数段のシフトレジスタ単位回路14の各々は、CK1信号がソース(S)またはドレイン(D)のうち一方に入力され、CK1信号を略反転したCK2信号がゲートに入力されるトランジスタTr3を含む。また、トランジスタTr3のゲート(G)にHレベルまたはLレベルのうち一方のCK2信号が入力されている場合には、トランジスタTr3のドレインにHレベルまたはLレベルのうち他方のCK1信号が入力されるように構成されている。

(もっと読む)

電気光学装置、シフトレジスタ回路および半導体装置

【課題】ゲート線駆動回路の領域を効率よく利用できると共に、ゲート線選択信号の立ち上がり速度の低下(立ち上がり遅延)を防止できる電気光学装置、並びに、それに適した単一導電型のトランジスタで構成されたシフトレジスタ回路を提供する。

【解決手段】ゲート線駆動回路30は、複数のゲート線GLの奇数行を駆動する奇数ドライバ30aと、偶数行を駆動する偶数ドライバ30bとから成る。奇数および偶数ドライバ30a,30bの単位シフトレジスタSRの各々は、2行前の選択信号Gk-2を受け、その2水平期間遅れて自己の選択信号Gkを活性化させる。偶数ドライバ30bのスタートパルスSP1は、奇数ドライバ30aのスタートパルスSP2よりも1水平期間だけ位相が遅れている。

(もっと読む)

記憶装置、半導体装置、及び電子機器

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。位相反転素子への電源電圧の印加を停止する場合、データを容量素子に記憶させることで、位相反転素子への電源電圧の供給を停止しても、容量素子においてデータを保持させる。

(もっと読む)

シフトレジスタ及び表示装置

【課題】シフトレジスタの消費電力を低減する。

【解決手段】第1の期間において第1の電圧状態であり、第2の期間乃至第4の期間において第2の電圧状態である第1のクロック信号が入力される第1のフリップフロップと、第2の期間の少なくとも一部において第1の電圧状態であり、第3の期間の少なくとも一部及び第4の期間において第2の電圧状態である第2のクロック信号が入力される第2のフリップフロップと、第1の期間、第2の期間、及び第4の期間において第2の電圧状態であり、第3の期間において第1の電圧状態である第3のクロック信号が入力される第3のフリップフロップと、第1の期間の少なくとも一部及び第2の期間において第2の電圧状態であり、第4の期間の少なくとも一部において第1の電圧状態である第4のクロック信号が入力される第4のフリップフロップと、を有する構成とする。

(もっと読む)

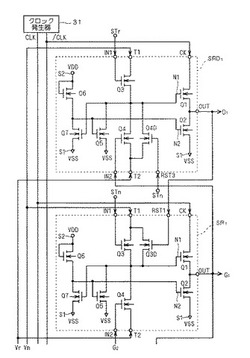

シフトレジスタ回路

【課題】シフトレジスタ回路において、外部からの初期化信号を必要とせずに各ノードのレベルを初期化でき、且つ、出力信号のレベル変化速度の低下を防止する。

【解決手段】シフトレジスタ回路は、クロック端子CKと出力端子OUTとの間に接続したトランジスタQ1、前段の出力信号Gk-1の活性化に応じてトランジスタQ1の制御電極(ノードN1)を充電するトランジスタQ3、ノードN1を放電するトランジスタQ5、トランジスタQ5の制御電極(ノードN2)を出力端とするインバータ、および、電源の遮断時にインバータの入力端(ノードN3)を放電し電源の投入後はオフするトランジスタQ8を備える。インバータの負荷素子であるトランジスタQ6は、電源の投入時にノードN2を充電する。

(もっと読む)

シフトレジスタ及び表示装置

【課題】シフトレジスタ又は該シフトレジスタを有する表示装置の消費電力を低減すること。

【解決手段】シフトレジスタは、クロック信号が1本の配線によって供給されるのではなく、複数の配線によって供給される。さらに、該複数の配線のいずれか一は、シフトレジスタの動作期間を通してクロック信号を供給するのではなく一部の期間においてのみクロック信号を供給する。そのため、クロック信号の供給に伴い駆動される容量負荷を低減することができる。その結果、シフトレジスタの消費電力を低減することができる。

(もっと読む)

シフトレジスタ回路、走査線駆動回路及び表示装置

【課題】単一導電型のトランジスタによって走査線をハイインピーダンス状態とし、パルスの立ち上がり及び立ち下り特性を向上させること。

【解決手段】1段シフトレジスタは、ドレイン電極が走査用配線に接続され、ソース電極が電源に接続された第1のトランジスタと、ドレイン電極が第1のトランジスタのゲート電極に接続され、ソース電極が前記電源に接続され、ゲート電極が第1の外部制御信号線に接続され、第1のトランジスタと同一の導電型の第2のトランジスタと、ドレイン電極が第2のトランジスタのドレイン電極に接続され、ソース電極が電源に接続され、ゲート電極がブートストラップ効果を用いるノードに接続され、第1のトランジスタと同一の導電型の第3のトランジスタと、一端が第2の外部制御信号線に接続され、他端が第2のトランジスタのドレイン電極に接続された負荷回路とを有する。

(もっと読む)

シフトレジスタ回路

【課題】リーク電流に起因する誤動作を防止することが可能なシフトレジスタ回路を提供する。

【解決手段】シフトレジスタ回路はその出力段に、出力端子OUT−第1クロック端子A間に接続するトランジスタT1、出力端子OUT−グラウンドGND間に接続するトランジスタT2を有する。トランジスタT2のゲートが接続するノードN2に接続したトランジスタT3は、ノードN2が充電されてトランジスタT2が導通状態になる期間に、第1クロック端子Aのクロック信号に同期してノードN2を充電し、リーク電流によるノードN2のレベル低下を補償する。

(もっと読む)

集積回路装置及び電子機器

【課題】 シリアルデータの遅延時間を減少可能な集積回路装置等を提供する。

【解決手段】 集積回路装置10は、第1〜第N(Nは2以上の整数)のレジスター121、・・・、12Nを有するシフトレジスター18であって、シリアルデータSDを入力し、第1〜第Nのレジスター121、・・・、12Nを介してシリアルデータSDを出力するシフトレジスター18と、シフトレジスター18の出力SRを保持し、シリアルデータSDを出力する専用レジスター19と、を含む。集積回路装置10は、専用レジスター19を介してシリアルデータSDを、カスケード接続される他の集積回路装置に出力信号SOとして出力する。

(もっと読む)

61 - 70 / 283

[ Back to top ]