国際特許分類[G11C19/00]の内容

国際特許分類[G11C19/00]の下位に属する分類

磁気素子を用いるもの (1)

共振回路中の非線型誘導素子を用いるもの

能動素子,例.放電管,半導体素子,と結合した磁気素子を用いるもの (1)

ステージの主素子としてキャパシタを用いるもの

放電管を用いるもの

半導体素子を用いるもの (202)

オプト―エレクトロニクス装置,すなわち電気的または光学的に結合された光放射および光―電気装置を用いるもの

超電導素子を用いるもの

3以上の異なる安定状態を有する記憶素子を用いるもの,例.電圧によるもの,電流によるもの,位相によるもの,周波数によるもの

二次元の,例.水平方向と垂直方向に情報が移動するシフト・レジスター

国際特許分類[G11C19/00]に分類される特許

81 - 90 / 283

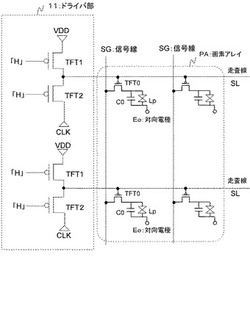

走査線駆動回路、表示装置及び走査線駆動方法

【課題】同一導電型のトランジスタで構成され、走査線を浮遊状態にすることが可能であって、出力パルス立ち上がり、立下り時間を短くする。

【解決手段】ソース電極を電源VDDに接続し、ドレイン電極を走査用配線SLに接続する第1のトランジスタTFT1と、ソース電極を走査用配線SLに接続し、ドレイン電極をクロック信号線CLKに接続する、第1のトランジスタTFT1と同一の導電型の第2のトランジスタTFT2と、を備え、第1および第2のトランジスタを同時にオフ状態となるバイアスを供給可能とするように構成する。ここでは、TFT1、TFT2共にNチャネルTFTとし、それぞれのゲート電極をハイ(H)レベルとすることで、TFT1、TFT2をオフ状態とする。

(もっと読む)

シフトレジスタ及び電子機器

【課題】シフトレジスタの消費電力を削減するとともに、動作を安定させる。

【解決手段】トランジスタT13〜T16によって、ノードAの電位Vaを反転させてノードBの電位VbとするインバータINVが構成される。前段のシフト回路からHighレベルの入力信号IN(k)が供給されると、ノードAの電位VaはHighレベルとなり、トランジスタT13がオンして、ノードBの電位VbはLowレベルとなる。電流は、電圧VHIのラインから、トランジスタT14,T15,T13を経由して、電圧VLWのアノードラインLaへと流れる。電圧VHIが印加される第2の端子P2とノードB間の電圧はトランジスタT14,T15によって分圧されて、各トランジスタのバイアス電圧が分圧される。従って、第2の端子P2とノードB間の抵抗の増加によってインバータINVに流れる貫通電流が低減されて消費電力が削減されるとともに、トランジスタT14、T15の閾値電圧のシフトが抑制されて、シフト回路21_kの動作が安定する。

(もっと読む)

両方向性電圧安定化を提供するディスプレイ装置

【課題】小型化可能な、両方向性安定化メカニズムを有するLCD装置等を提供する。

【解決手段】LCD装置は、複数のゲートラインと、対応するゲートラインを駆動する複数のシフトレジスタとを有する。各シフトレジスタは第1回路及び第2回路を有する。第1回路は、対応するゲートラインの第1の側に配置されており、パルス発生器と、第1W/L比を有する第1トランジスタとを有する。パルス発生器は、ノードで得られる電圧に従って駆動信号を供給し、一方、第1トランジスタはノードの電圧レベルを保つ。第2回路は、対応するゲートラインの第2の側に配置されており、第2W/L比を有する第2トランジスタを有する。第2トランジスタは、対応するゲートラインの第2の側からの駆動信号の電圧レベルを保つ。第1W/L比は第2W/L比より小さく、第1回路は第2回路より大きい空間を占有する。

(もっと読む)

駆動回路、表示装置、及び電子機器

【課題】トランジスタの劣化を抑制する。

【解決手段】第1薄膜トランジスタ乃至第11トランジスタで構成される複数のパルス出力回路を構成し、各トランジスタを制御する複数のクロック信号、前段のパルス出力回路より入力される前段信号、後段のパルス出力回路より入力される後段信号、及びリセット信号に基づいて動作させる。そして当該薄膜トランジスタのチャネル領域となる半導体層を微結晶半導体で構成する。そして、薄膜トランジスタの特性劣化の程度を小さくできる。

(もっと読む)

ゲート駆動装置及びこれを含む表示装置

【課題】静電気に対する耐性が強いゲート駆動装置及びこれを含む表示装置を提供する。

【解決手段】第1乃至第(n+1)(nは自然数)ステージを有するゲート駆動装置であって、第nゲート出力信号を出力する第nステージと、第(n+1)ゲート出力信号を出力する第(n+1)ステージとを有し、前記第nステージと第(n+1)ステージは順次に配置され、前記第nステージは、ゲート電極、ソース電極、及びドレイン電極を含み、前記ゲート電極は前記第(n+1)ゲート出力信号の印加を受けるトランジスタと、ダミーゲート電極、ダミーソース電極、及びダミードレイン電極を含み、前記ダミーソース電極は前記トランジスタの前記ソース電極又は前記ドレイン電極と接続され、前記第1ステージに流入する静電気を防止するダミートランジスタとを含む。

(もっと読む)

シフトレジスタ用回路並びにこれを用いたシフトレジスタ及び画像表示装置

【課題】無比率型論理回路で構成されるシフトレジスタの各段に、負荷側で必要な電圧(出力用電圧)を出力するための出力回路が設けられたシフトレジスタにおいて、いずれかの段の出力端子に接続される負荷側で故障が発生しても、その故障による次段への影響を少なくする。

【解決手段】この回路は、シフトレジスタにおける1つの段の回路であり、TFTQ8,Q9のソース端子には電源電圧Vb,Vcが印加され、これらのドレイン端子には共通の外部出力端子が接続され、これらのゲート端子には状態選択信号が同一タイミングで入力される。第1同期反転回路及び第2同期反転回路から出力される信号から、互いに共役関係となる2つの状態選択信号がそれぞれ生成され、生成した各状態選択信号が2つのTFTQ8,Q9のゲート端子へ出力される。

(もっと読む)

シフトレジスタならびにそれを備えた走査信号線駆動回路および表示装置

【課題】走査信号線の走査順序の切り替えが可能なシフトレジスタを回路面積の増大や消費電流の増大を抑制しつつ実現する。

【解決手段】シフトレジスタを構成する各段は、出力端子61の電位を第1クロックCKAに基づいて上昇させるための薄膜トランジスタTSと、薄膜トランジスタTSのゲート端子に接続された領域netAの電位を前段/後段から出力される状態信号に基づいて上昇させるための薄膜トランジスタT1/T2と、領域netAの電位を次々段/前々段から出力される状態信号に基づいて低下させるための薄膜トランジスタT3/T4とを備える。シフトレジスタの初段については、外部から与えられる第1のゲートスタートパルス信号に基づいて領域netAが充電され、シフトレジスタの最終段については外部から与えられる第2のゲートスタートパルス信号に基づいて領域netAが充電される。

(もっと読む)

シフトレジスタ駆動方法並びにシフトレジスタ及びこれを備える液晶表示装置

【課題】大画面、高解像度のa−Si TFT LCDに適用可能にする。

【解決手段】シフトレジスタ270は、縦続接続された複数のステージにより構成され、各ステージのキャリー電圧を発生するキャリーバッファ部を内蔵する。各ステージのプルダウントランジスタを所定のサイズ比を有する第1及び第2プルダウントランジスタ2個に分離する。また、シフトレジスタにクロック発生器に提供された電圧源(Von)よりさらに大きい電圧源(Vona)を提供する。大画面、高解像度のa−Si TFT LCDに適用時にRC遅延を最少化することができ、臨界電圧に鋭敏ではないシフトレジスタを提供することができ、その結果、画面表示不良が発生されない高解像度の大画面ディスプレイを具現することができる。

(もっと読む)

シフトレジスタ回路、基本回路および表示装置

【課題】各転送段での転送動作ごとに回路に貫通電流が流れるため、シフトレジスタ回路全体の消費電力が大きくなる。

【解決手段】前段、後段のレジスタ(転送段)の各出力を入力IN1,IN2とすることによって転送動作を行うシフトレジスタ回路において、入力IN1として前段(n−1)の出力OUT(n−1)が与えられたとき、ブートストラップ状態確定回路22の作用により、MOSトランジスタQp15のゲート電位をVDD電位に設定し、MOSトランジスタQp16のゲート電位をVSSの電位に設定する。また、ブートストラップ状態以外では、入力IN2として後段(n+1)の出力OUT(n+1)が与えられることで、初期状態確定回路21の作用により、MOSトランジスタQp15のゲート電位をVSS電位に設定し、MOSトランジスタQp16のゲート電位をVDD電位に設定する。

(もっと読む)

電子機器及びシフトレジスタの制御方法

【課題】ゲートドライバのシフトレジスタの出力を安定化させる。

【解決手段】ゲートドライバ12は、n段のシフト回路が直列に接続されたシフトレジスタを備え、各シフト回路は出力信号OUT(1)〜OUT(n)を出力する。コントローラ14は、このゲートドライバ12に、スタート信号Start1、クロック信号ck1,ck2を供給し、また、出力信号OUT(n)を出力した直後から次の出力信号OUT(n−1)を出力する直前まで、Highレベルの出力信号OUT(n)の電位を変位させるend信号を供給する。この出力信号OUT(n)の電位が変位することにより、最終段のシフト回路の動作が安定し、後段から順次動作が是正され、予め設定された期間が経過したときは、すべての段のシフト回路が安定し、正常動作状態に落ち着く。

(もっと読む)

81 - 90 / 283

[ Back to top ]