国際特許分類[G11C19/28]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 情報がステップ形式で移動するデジタル記憶装置,例.シフト・レジスター (487) | 半導体素子を用いるもの (202)

国際特許分類[G11C19/28]に分類される特許

1 - 10 / 202

シフトレジスタ回路

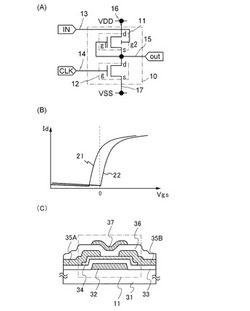

【課題】トランジスタのしきい値電圧の制御を行いながら、ゲート電極の電位は変動させず、バックゲート電極の電位のみを変動させることで、入力信号に応じた信号を出力することが可能な論理回路を有するシフトレジスタ回路を提供する。

【解決手段】同じ導電型の第1のトランジスタ及び第2のトランジスタを有する論理回路、を含むシフトレジスタ回路において、第1のトランジスタの第1のゲート電極を、第1のトランジスタのソース電極またはドレイン電極に接続し、第1のトランジスタの第2のゲート電極に入力信号を供給し、第2のトランジスタのゲート電極にクロック信号を供給し、第1のゲート電極と、ゲート電極とは、同じ層とする。

(もっと読む)

シフトレジスタ

【課題】シフトレジスタ動作を小さいチップ面積で実現可能とし且つクロック入力の立ち上がり(もしくは立ち下がり)エッジのみで動作可能とするシフトレジスタを提供する。

【解決手段】制御信号CK(36)がLで制御信号CKb(37)がHのとき、スイッチ12を経て入力信号D(11)はラッチセル13のインバータ14に加えられ、インバータ14の出力信号がラッチセル13の出力としてインバータ16で反転されてシフト出力Q0(17)となる。スイッチ18は制御信号CKb(37)が立ち下がる時点、すなわちクロック入力CK_in(34)の立ち上がり時点で動作してラッチセル13の出力を通過させ、ラッチセル19のインバータ20に加え、インバータ20の出力信号がラッチセル19の出力としてシフト出力Q1(22)となる。以下同様に、スイッチ23,29及びラッチセル24,30を経て入力信号D(11)がシフト出力Q2(28),Q3(33)に次々と伝搬される。

(もっと読む)

半導体装置

【課題】単極性のTFTを用いて構成するデジタル型式の表示装置において、消費電流を低減することの出来る回路を提供する。

【解決手段】デジタル映像信号の保持を行うラッチ回路であって、TFT101の入力電極にデジタル映像信号が入力されると、TFT101の出力電極からは非反転出力信号が出力され、TFT102およびTFT103の出力電極からは反転出力信号が出力されるラッチ回路を提供する。出力を非反転、反転の2系統得られるため、後段のバッファを駆動する際に、電源間の直流パスが生ずる期間を短くすることが出来、消費電流の低減に寄与する。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバI

Cの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化

を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジス

タを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電

位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック

信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力

することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給

する。

(もっと読む)

シフトレジスタ及びこれを用いたゲート駆動回路

【課題】既存構造に比べて構成要素を減少させつつ、動作信頼性を向上させる。

【解決手段】複数のシフトレジスタの夫々が、該シフトレジスタの前段または後段のシフトレジスタの出力信号によって方向入力信号を第1のノードに出力する入力部と、第2のクロック信号によって制御され、第1のノードに接続されて第1のノードの信号に対する反転信号を発生させて第2のノードに出力するインバータ部と、第1のノードと接続され第1のクロック信号に同期して第1のノードの信号により第1のクロック信号を活性化させて当該ゲートラインに出力信号を出力するプルアップ部及び第2のノードの信号によりプルダウン出力信号を活性化させて当該ゲートラインに出力信号を出力するプルダウン部からなる出力部と、第1のノードを第2のクロック信号によって周期的にリセットするリセット部とを備える。

(もっと読む)

半導体装置、シフトレジスタ、表示装置

【課題】非選択期間においてノイズが少なく、且つトランジスタを常時オンすることのない半導体装置、シフトレジスタ回路を提供することを目的とする。

【解決手段】第1〜第4のトランジスタを設け、第1のトランジスタの、ソースとドレインのうち一方を第1の配線に接続し、他方を第2のトランジスタのゲート電極と接続し、ゲート電極を第5の配線に接続し、第2のトランジスタの、ソースとドレインのうち一方を第3の配線に接続し、他方を第6の配線に接続し、第3のトランジスタの、ソースとドレインのうち一方を第2の配線に接続し、他方を第2のトランジスタのゲート電極に接続し、ゲート電極を第4の配線に接続し、第4のトランジスタの、ソースとドレインのうち一方を第2の配線に接続し、他方を第6の配線に接続し、ゲート電極を第4の配線に接続する。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

論理回路および半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

(もっと読む)

半導体装置

【課題】電流駆動能力がより小さなクロック信号生成回路を適用することが可能な半導体装置を提供する。

【解決手段】nチャネル型トランジスタで構成されるスイッチ及び論理回路を有し、スイッチは導通状態又は非導通状態がクロック信号によって選択され、論理回路は、ブートストラップ回路と、入力信号が入力される入力端子と、反転入力端子と、出力端子とを有し、高電源線と出力端子との接続を反転入力端子に入力される信号によって制御し、低電源線と出力端子との接続を入力端子に入力される信号によって制御することによって、入力信号がローレベル電位の場合には、ブートストラップ回路を用いて出力端子の電位を上昇させることにより出力端子から高電源電位を出力し、トランジスタは、チャネルが形成される半導体層と、半導体層を挟んで上下に設けられた一対のゲート電極とを有し、一対のゲート電極の他方はソースと接続される。

(もっと読む)

パルス信号出力回路およびシフトレジスタ

【課題】安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供する。

【解決手段】酸化物半導体を用いたトランジスタを複数用いて、パルス信号出力回路を構成する。また、パルス信号出力回路の動作に応じて、酸化物半導体を用いたトランジスタのしきい値電圧を変動させる。また、該パルス信号出力回路を含むシフトレジスタを構成する。これにより、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

1 - 10 / 202

[ Back to top ]