国際特許分類[G11C27/00]の内容

国際特許分類[G11C27/00]の下位に属する分類

国際特許分類[G11C27/00]に分類される特許

1 - 10 / 13

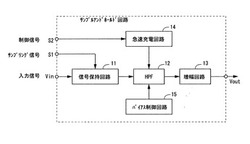

サンプルアンドホールド回路

【課題】ハイパスフィルタ回路を急速充電できるようにして、その起動時間を短くする。

【解決手段】所定のタイミング毎に入力信号を保持する信号保持回路11と、信号保持回路11の出力側に接続された第1のトランジスタQ1の出力側の第1のノードN1に現れる信号から低域成分を除去するハイパスフィルタ回路12と、起動時にのみ動作してハイパスフィルタ回路12のコンデンサC2に対して急速充電を行う急速充電回路14と、ハイパスフィルタ回路12の出力側に接続された増幅回路13と、急速充電回路14による急速充電動作の終了から通常動作に移行する前後で前記第1のノードN1のバイアス電位をほぼ一定に保持するバイアス制御回路15とを備える。

(もっと読む)

ホールド回路

【課題】広い動作電圧範囲で精度よく動作するホールド回路の提供。

【解決手段】入力信号端子と、出力電圧出力端子と、非反転入力端子に入力信号端子が接続された増幅器と、入力端子に増幅器出力端子が接続された反転増幅器と、一端に増幅器反転入力端子が接続され他端に基準電位が接続されたキャパシタと、入力端子にキャパシタの一端が接続されたバッファ回路と、ゲートに増幅器出力端子が接続されソースにバッファ回路出力端子が接続されバルクに電圧源が接続された第1トランジスタと、ゲートに反転増幅器出力端子が接続されソースおよびバルクに電圧源が接続されドレインに第1トランジスタドレイン端子が接続された第2トランジスタと、ゲートに反転増幅器出力端子が接続されソースおよびバルクに第1トランジスタドレイン端子と第2トランジスタドレインとが接続されドレインにキャパシタの一端が接続された第3トランジスタと、を有するホールド回路。

(もっと読む)

ホールド回路

【課題】保持電圧の下降または上昇傾きを良好に調整可能なホールド回路を提供すること。

【解決手段】ホールド回路10は、入力端子20、第1出力端子22、基準電圧端子24、オペアンプ30、ダイオード32、コンデンサ36、抵抗R0、電圧発生回路50、を備えている。コンデンサ36は、一端が接続点26に接続され、他端が基準電圧端子24に接続される。抵抗R0は、一端が接続点26に接続される。ダイオード52のアノードが、オペアンプ38を介して接続点26に接続される。抵抗R0の他端と中間接続点58とが接続される。オペアンプ30は、非反転入力端子30bが入力端子20に接続され、反転入力端子30aが接続点26に接続され、出力端子30cがダイオード32に接続される。電圧発生回路50は、ダイオード52に入力される出力電圧V22から変化させたオフセット電圧V23を生成して、中間接続点58から出力する。

(もっと読む)

サンプルホールド回路

【課題】S/N比を向上させたサンプルホールド回路を提供すること。

【解決手段】入力電圧を入力する入力端子と、入力電圧に基づいたサンプリング電圧をホールドする複数の容量と、入力端子と記複数の容量との間に夫々接続された複数の入力スイッチと、複数の容量のホールド電圧を出力する出力端子と、を備え、複数の容量は、複数の入力スイッチによって異なるタイミングで入力電圧をサンプリングし、複数の容量のホールド電圧の平均化処理を行って出力端子に出力する、構成とした。

(もっと読む)

ピークホールド回路のリセット装置

【課題】安価な構成で適切なタイミングにリセット信号を出力させる。

【解決手段】A/D変換回路3からデジタル信号として入力されるホールドコンデンサCのホールド電圧の電圧レベルの増加を検出したときに、増加前後の電圧レベルの差をコンパレータ5aによって求める。そして、求めた差が所定のしきい値以下である場合は、リセット信号を出力する。よって、入力信号Vinの入力に伴うホールドコンデンサCのホールド電圧の増加量が、ホールド電圧の飽和判断に適した所定のしきい値以下になった時点で、初めてホールドコンデンサCをリセットしてホールド電圧を放電させる。これにより、ホールドコンデンサCの1回目のチャージ時点におけるホールド電圧に比べてはるかに、入力信号Vinの反転信号の電圧レベルのピーク値に近い値にホールド電圧が達するまで、ホールドコンデンサCをチャージさせた時点で、リセット信号を確実に出力することができる。

(もっと読む)

サンプルアンドホールド回路

【課題】製造ばらつきや、温度変化により、ローパスフィルタの特性ばらつきや特性変動が発生するという課題があった。また、低い周波数ノイズ除去で回路チップが大きくなるという課題があった。これら課題を解決するサンプルアンドホールド回路を提供する。

【解決手段】本発明のサンプルアンドホールド回路は、外部電気信号が入力されるための信号入力端子と、内部電気信号を出力するための信号出力端子と、外部電気信号に起因する電荷を蓄積するよう信号入力端子に接続された第1の電荷蓄積手段と、第1の電荷蓄積手段に接続され、電荷を第1の電荷蓄積手段との容量の比に応じて分配蓄積可能とする第2の電荷蓄積手段と、第1の電荷蓄積手段に電荷を蓄積することと、電荷の分配蓄積ならびにこれに起因する内部電気信号を信号出力端子に出力することとを切り替え制御する制御手段とを有する。

(もっと読む)

ドループ補正ピークホールド回路

【課題】ピークホールド回路において、ドループを抑制してピーク電圧を長時間保持できるドループ補正ピークホールド回路を提供すること。

【解決手段】ピークホールド回路のホールドコンデンサC1は、一端をダイオードD1のカソードに接続し、他端をドループ補正回路20に接続してある。ドループ補正回路20は、ホールドコンデンサC2の保持電圧を、増幅回路A3において極性を反転してホールドコンデンサC1に印加する。即ちドループ補正回路20は、ホールドコンデンサC1にその保持電圧と逆極性のドループ補正電圧を印加する。ドループ補正電圧の印加によりホールドコンデンサC1のドループを長時間抑制できる。

(もっと読む)

信号値保持装置、信号値保持方法、信号値制御システム、信号値制御方法、再生装置、および再生方法

【課題】入力信号に対する応答性を向上しつつ、実際の入力信号のピーク値と保持する信号値の差分を減少させることが可能な、信号値保持装置、信号値保持方法、信号値制御システム、信号値制御方法、再生装置、および再生方法を提供する。

【解決手段】入力信号の信号値と所定の帰還信号の信号値の大小関係を判断する判断部と、前記判断部により大きいと判断された方の信号値を保持する第1の保持部と、前記第1の保持部に保持されている信号値から所定値を減じて前記帰還信号として出力する減算部240と、前記第1の保持部に保持されている信号値が入力され、前記判断部による前記信号値の大小関係の判断結果に基づき、前記入力信号の信号値の方が前記帰還信号の信号値より小さくなる際に前記第1の保持部から入力された信号値を保持する第2の保持部と、を備える信号値保持装置。

(もっと読む)

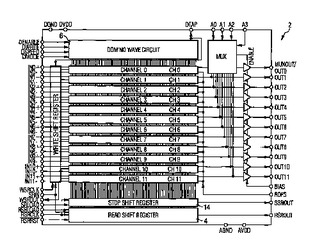

波形デジタイジングに対する高速読み出し法およびスイッチトキャパシタアレイ

本発明に記載されているのは、スイッチトキャパシタアレイ(SCA)回路の読み出し時間を短縮する技術である。実現可能であるのは、10MSPS〜5GSPSのサンプリング速度で12個の差分入力チャネルをサンプリング可能なSCAチップである。アナログ波形は、チャネル当たりに1024個のサンプリングセルに記憶することができ、また33MHzでクロック制御されるシフトレジスタを介してサンプリングした後、読み出して外部でデジタイゼーションすることができる。上記のサンプリングセルに対する書き込み信号は、チップに形成される一連のインバータ(ドミノ原理)によって生成される。上記のドミノ波は、トリガによってストップされるまで連続して伝わる。読み出しシフトレジスタ4は、クロックに同期して多重化出力部MUXかまたは個別出力部のいずれかに上記のサンプリングセルの内容を出力し、これはここで外部ADCによってデジタイズすることができる。上記の波形の一部だけを読み出してデジタイゼーション時間を短縮することができる。高いチャネル密度、450MHzの広いアナログ帯域幅および(オフセット較正後の)0.35mVの低ノイズによってこのチップは、低出力、高速、高精度の波形デジタイジングに理想的に適合する。先進のCMOSプロセスにおいて放射に強い設計で作製すれば、本発明のチップは、64リードのLQFP(low profile quad flat pack)および64ピンのQFN(quad flat non-leaded package)で利用可能である。  (もっと読む)

(もっと読む)

サンプル・ホールド回路

【課題】サンプリング精度を向上できるサンプル・ホールド回路をを提供する。

【解決手段】第1の動作モードにおいて、キャパシタ1には、入力端子Tinに入力される信号電圧VINからオフセット電圧VOFSTを差し引いた電圧が印加される。第2の動作モードになると、演算増幅器OP1には、キャパシタ1に保持される電圧VSMPが入力される。そのため、第2の動作モードでは、キャパシタ1に保持される電圧VSMPにオフセット電圧VOFSTを足し合わせた電圧が、演算増幅器OP1から出力される。このとき、キャパシタ1には、信号電圧VINからオフセット電圧VOFSTを差し引いた電圧VSMPが保持されているため、これにオフセット電圧VOFSTを足し合わせた電圧は、第1の動作モードにおいて入力端子Tinに入力される信号電圧VINとほぼ等しくなる。

(もっと読む)

1 - 10 / 13

[ Back to top ]