国際特許分類[G11C29/00]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 正確な動作のための記憶装置のチェック;スタンバイまたはオフライン動作中の記憶装置のテスト (2,382)

国際特許分類[G11C29/00]の下位に属する分類

故障した周辺回路の検出またはその位置の特定 (62)

故障したメモリ素子の検出またはその位置の特定 (1,973)

メモリ内容の保護;メモリ内容の誤りの検出

試験回路を設計するための装置,例.テスト容易化設計ツール

静的記憶のための外部試験装置,例.自動検査装置;そのインターフェース (267)

国際特許分類[G11C29/00]に分類される特許

1 - 10 / 80

メモリコントローラ

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置

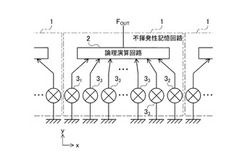

【課題】不揮発性記憶回路の出力として「未破壊」を示す第1の論理レベルが期待される場面で、第1及び第2の不揮発性記憶素子の一方に干渉破壊が発生したとしても、第3の不揮発性記憶素子に干渉破壊が生じない限り、不揮発性記憶回路に正しく第1の論理レベルを出力させる。

【解決手段】半導体装置は、第1及び第2の不揮発性記憶素子31,32と、少なくとも1つの第3の不揮発性記憶素子33と、少なくとも1つの第3の不揮発性記憶素子33すべてと、第1及び第2の不揮発性記憶素子31,32のうちの少なくともいずれか一方とが未破壊状態である場合に、未破壊を示す第1の論理レベルを出力する論理演算回路2とを有する不揮発性記憶回路1を備える。

(もっと読む)

半導体装置

【課題】複数の貫通電極を選択的に利用可能な積層型の半導体装置において、回路動作を安定させる。

【解決手段】半導体記憶装置10は、インターフェースチップIFと複数のコアチップCCを含む。コアチップCCは、インターフェースチップIFに積層される。インターフェースチップIFとコアチップCCは複数の貫通電極TSVにより接続される。コアチップCCに含まれる入力切り替え回路240、230は、電源投入時における設定処理の前に、コアチップCCに含まれる複数の入力信号線と複数の貫通電極TSVとの接続をいったん遮断し、コアチップCCの設定後に、複数の入力信号線と複数の貫通電極TSVの接続を示す救済情報にしたがって各入力信号線を複数の貫通電極TSVのいずれかと接続する。

(もっと読む)

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

半導体ディスク寿命監視装置

【課題】不揮発性の半導体ディスクの寿命を監視する半導体ディスク寿命監視装置を提供する。

【解決手段】半導体ディスク5−1〜5−Kの書込み制御を行うファイルシステム3と、当該ファイルシステム3と前記半導体ディスク5−1〜5−Kを接続するインタフェースドライバ4を備え、当該インタフェースドライバ4により書込みが行われる半導体ディスク5−1〜5−Kの寿命を予測する半導体ディスク寿命監視装置1であって、前記ファイルシステム3からの書込みを書込情報として測定する測定部7と、前記測定結果を累積し第1の保存データ32として保存する保存部8と、前記保存した累積書込情報に基づいて、半導体ディスク5−1〜5−Kの寿命を予測する。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】ロールコールテストに要する工数を削減できる半導体記憶装置及びそのテスト方法を提供する。

【解決手段】不良アドレスが格納される不揮発性の記憶素子を備えた半導体記憶装置にロールコールテスト時にマスク用テストモード信号を出力するテスト制御回路とロールコール回路とを備える。ロールコール回路は、アドレス信号と不良アドレスとをビット単位で比較し、その比較結果を出力する。また、ロールコール回路は、マスク用テストモード信号が入力されると、アドレス信号の所望のビットに対応する比較結果をマスクして上記アドレス信号と不良アドレスとが一致していることを示す値を出力すると共に、マスクされていないビットに対するロールコールテストを可能にする。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

メモリシステム

【課題】不良メモリチップが発生した場合でも、並列駆動可能な組み合わせ数を最大限確保可能なメモリシステムを提供すること。

【解決手段】物理バンク内の不良メモリチップが識別可能な不良メモリチップ情報に基づき、不良メモリチップを使用せずに各レーン内において並列アクセス可能なメモリチップ数が最大となるように、論理バンクを構成する複数の物理バンクの組み合わせを動的に設定する。

(もっと読む)

不揮発性半導体記憶装置

【課題】不良ブロック情報を適切に管理することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は不揮発にデータを記憶する複数のメモリセルを配列してなる複数のブロック、並びにメモリセルと接続されるワード線、及びビット線を有するメモリセルアレイと、メモリセルアレイ内に設けられ、ブロックが不良ブロックであること示す不良ブロック情報を不揮発に記憶可能に構成された不良ブロック格納領域と、ワード線を選択するロウデコーダと、メモリセルに対するデータの書き込み、消去及び読み出しを制御する制御回路とを備える。制御回路は、不良ブロック格納領域に書き込まれた不良ブロック情報をビット線を介して外部へ出力する出力動作を実行可能に構成されるとともに、外部から入力された不良ブロック情報をビット線を介して不良ブロック格納領域に書き込む第1の書き込み動作を実行可能に構成される。

(もっと読む)

データ生成装置

【課題】簡易な構成で、不良カラムを置き換えたデータを生成可能なデータ生成装置を提供する。

【解決手段】第1記憶部50と第2記憶部36と入力部と出力部65とを含む。第2記憶部は、所定数よりも多い数の記憶領域が直列に接続される。入力部は、ホスト装置から送られるデータを所定数ずつ第2記憶部へ入力する。シフト数決定部66は、欠陥のあるデータ線の数に応じた値を示すシフト数を決定する。出力部は、セクタの識別情報に対応する欠陥情報に基づいて、先頭の記憶領域よりもシフト数だけ後の記憶領域から順番に、当該記憶領域に格納されたデータを、当該セクタ内の欠陥の無いデータ線へ供給するデータとして出力する一方、データとは別の所定情報を、当該セクタ内の欠陥のあるデータ線へ供給するデータとして出力することで、当該セクタに供給される書き込みデータを出力する。

(もっと読む)

1 - 10 / 80

[ Back to top ]