国際特許分類[G11C5/00]の内容

国際特許分類[G11C5/00]の下位に属する分類

記憶素子の配置,例.マトリックス配列におけるもの (1)

記憶素子を電気的に相互結合する機構,例.ワイヤリング (1)

記憶素子を相互結合するために用いる装置または方法,例.磁心に線を通すためのもの

電力供給装置 (4)

国際特許分類[G11C5/00]に分類される特許

1 - 10 / 102

半導体装置

【課題】複数の貫通電極を選択的に利用可能な積層型の半導体装置において、回路動作を安定させる。

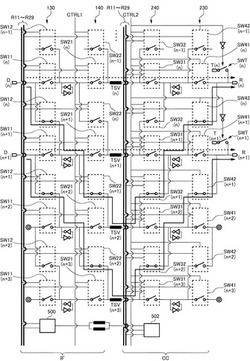

【解決手段】半導体記憶装置10は、インターフェースチップIFと複数のコアチップCCを含む。コアチップCCは、インターフェースチップIFに積層される。インターフェースチップIFとコアチップCCは複数の貫通電極TSVにより接続される。コアチップCCに含まれる入力切り替え回路240、230は、電源投入時における設定処理の前に、コアチップCCに含まれる複数の入力信号線と複数の貫通電極TSVとの接続をいったん遮断し、コアチップCCの設定後に、複数の入力信号線と複数の貫通電極TSVの接続を示す救済情報にしたがって各入力信号線を複数の貫通電極TSVのいずれかと接続する。

(もっと読む)

半導体装置

【課題】データ用電流パスの占有面積を最小化し、かつ動作速度の低下も抑制する。

【解決手段】半導体装置10は、互いに積層されたインタフェースチップIF及び複数のコアチップと、インタフェースチップIFと複数のコアチップのそれぞれとを接続するデータ用電流パスとを備え、インタフェースチップIFは、複数のコアチップに対して同時にリードコマンドを供給するコマンドデコーダ32を有し、複数のコアチップはそれぞれ、メモリセルアレイ50と、当該コアチップに割り当てられた層アドレスLIDを記憶する層アドレス発生回路46と、リードコマンドに応じてメモリセルアレイ50からリードデータを読み出し、層アドレス発生回路46に記憶される層アドレスLIDに応じたタイミングで、上記データ用電流パスを介してインタフェースチップIFに出力するデータコントロール回路54とを有する。

(もっと読む)

半導体装置

【課題】不要にリフレッシュ周期が変更されることによる無駄な消費電流を削減する。

【解決手段】複数の半導体チップを備え、複数の半導体チップのうちの第1の半導体チップは第1の温度センサを有し、第1の半導体チップとは異なる第2の半導体チップはリフレッシュ動作を必要とする半導体チップであって、第1の半導体チップの第1の温度センサの出力結果に応じて第2の半導体チップのリフレッシュ周期が変更される。

(もっと読む)

半導体装置

【課題】被制御チップの出力回路から制御チップの入力回路へ伝送されるデータ信号の位相を、入力回路に供給される同期信号の位相に一致させる。

【解決手段】半導体装置は、第1の被制御チップ110とそれと積層する制御チップ120を備える。第1の被制御チップは、同期信号に応じてデータ信号を出力する第1の回路117と、そのデータ信号を遅延同期信号に同期してデータ端子へ出力する入出力回路118と、出力回路を模した回路であって、遅延同期信号に同期してレプリカ信号を第1のレプリカ端子へ出力するレプリカ回路119とを含む。制御チップは、同期信号を出力し、データ信号を受ける第1の制御回路126と、同期信号を遅延させて遅延同期信号として出力する遅延調整回路130と、レプリカ信号の位相と同期信号の位相とを比較する位相比較回路128と、位相比較回路の比較結果に基づいて遅延調整回路の遅延量を制御する遅延制御回路129とを含む。

(もっと読む)

半導体装置

【課題】半導体チップに構成されるメモリコアにおける電源系を容易に分離可能な配線構造を実現しスループットの向上が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体チップC1に複数のメモリコア(DRAMコア)が構成される。各メモリコアは、第1電源によって動作しパラレルデータを双方向に伝送するデータバスを駆動する第1回路領域と、第1電源と分離された第2電源によって動作しデータバスを伝送されるパラレルデータと外部端子を介して入出力されるシリアルデータとを双方向に変換する第2回路領域と含む。第1貫通電極群23は、第1回路領域に第1電源を供給する複数の貫通電極をY方向に並べて配置され、第2貫通電極群21は、第2回路領域に第2電源を供給する複数の貫通電極をY方向と交差するX方向に並べて配置される、それぞれの貫通電極群を経由して第1及び第2電源の配線群が互いに分離した配置で形成される。

(もっと読む)

メモリ装置

【課題】大容量化が容易であり、高収率且つ高信頼性を有する半導体メモリ装置が提供される。

【解決手段】本発明に従うメモリ装置は、記憶素子と前記記憶素子にデータを書き込むか、又は読み出す周辺回路を含む第1半導体チップ、及び外部と前記第1半導体チップとの間で交換されるデータ又は信号の入出力機能を遂行する第2半導体チップを含み、本発明のその他の特徴に従うメモリ装置は、外部とデータ又は信号を交換するための入出力回路チップ、及び各々前記入出力回路チップから提供される信号に応答して前記データを格納するか、或いは内部に格納されたデータを読み出して前記入出力回路チップへ出力する、垂直方向に積層される複数のコアチップを含む。

(もっと読む)

半導体装置

【課題】信号伝送のより高速化を図る。

【解決手段】入力信号Vinと基準信号Vrefとを入力する第1の差動対(Q3、Q4が相当)と、第1の差動対のそれぞれ負荷となる第1及び第2のトランジスタQ2、Q1と、を含む第1の入力回路を備え、第1の入力回路の出力側となる第1のトランジスタQ2は、第2のトランジスタQ1に比べてゲート幅を長くする。

(もっと読む)

半導体装置

【課題】消費電力の低減と干渉の抑制を実現できる半導体装置を提供する。

【解決手段】半導体装置は、直列に多段接続された第1及び第2のチップと制御チップとを備える。第1及び第2のチップのそれぞれの転送制御部は、識別信号が制御チップから供給されると当該識別信号後段のチップへ伝送し、制御チップが供給するクロック信号のn番目のパルスに基づいて、識別信号が表す識別情報を第2の記憶領域に書き込み、書き込みが終了するまでクロック信号の後段のチップへの伝送を阻止する。制御チップは、コマンドによって第1及び第2のチップを排他的にアクセスし、第1及び第2のチップのスイッチ制御回路は、コマンド及び識別情報に応じてそれぞれ対応する第1のスイッチ回路を互いに排他的に制御する。

(もっと読む)

半導体モジュール及びモジュール基板

【課題】モジュール基板の短辺方向における搭載マージンを確保しつつ、モジュール基板に形成する配線の低密度化及び等長化を図る。

【解決手段】モジュール基板20と、モジュール基板20に搭載された複数の半導体装置、例えばDRAM101〜136とを備える。X方向に隣接する2つのDRAMの搭載方向は互いに180°異なっており、Y方向に隣接する2つのDRAMの搭載方向も互いに180°異なっている。これにより、斜め方向に位置するDRAMをフライバイ方式で接続すれば、モジュール基板20に設ける配線の低密度化及び等長化を図ることが可能となる。

(もっと読む)

半導体装置

【課題】チップ間の貫通電極(TSV)の数を増やすことなく、任意の数のチップに対して識別番号を割り付ける。

【解決手段】本発明による半導体装置は、積層された複数のチップを備えた半導体装置であって、前記複数のチップのうちの一つのチップが、所定の信号に基づきパルス信号を発生させて隣接チップに供給するパルス発生部(1100)を備え、前記複数のチップのうち、前記一つのチップを除く各チップが、一方の隣接チップからパルス信号が供給され、該パルス信号のパルスの数を変更して他方の隣接チップに供給するパルス変更部(2200)と、前記パルス信号のパルスの数に応じてチップの識別番号を表す識別信号を発生する識別信号発生部(2100)を備える。

(もっと読む)

1 - 10 / 102

[ Back to top ]