国際特許分類[H01L21/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847)

国際特許分類[H01L21/00]の下位に属する分類

半導体装置またはその部品の製造または処理 (125,986)

半導体装置以外の固体装置またはその部品の製造または処理であって,グループ31/00〜51/00に分類されている一つの型の装置に特に適していないもの (1)

製造または処理中の試験または測定 (6,126)

製造または処理中の半導体または電気的固体装置の取扱いに特に適用される装置;半導体または電気的固体装置もしくは構成部品の製造または処理中のウエハの取扱いに特に適用される装置 (11,346)

1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275)

国際特許分類[H01L21/00]に分類される特許

41 - 50 / 113

半導体デバイスの応力のモデリング方法およびシステム

【課題】半導体デバイスの応力をモデリングする方法を提供する。

【解決手段】コンパクト・モデル内のモデル・パラメータの正確さを改善する計算方法は、応力モデルを、ベース・モデルを生成するデータセットに再フィッティングすることによって、独立に形成されたベース・モデルと応力モデルを矛盾が無いように適合させるための方法及びアルゴリズムを用いる(310、320)。再フィッティング・アルゴリズムは、応力モデルが寸法スケーリング・マクロから取得されるデータセットに適用されるので、ベース・モデルと応力モデルの間のあらゆる不一致を除去する。寸法スケーリング・マクロのデバイスに関する応力オフセットは、同じデバイスのモデル・パラメータの測定値にフィットするように計算される(340)。モデル・パラメータを寸法スケーリング・マクロからのデータセットにフィッティングするプロセスは、モデル・パラメータに関する定数、1次及び2次係数を計算し、これらが回路のシミュレーション及び最適化に用いられるモデル・パラメータ及びコンパクト・モデルの正確さを増すように用いられる(360)。

(もっと読む)

マスクレイアウトパラメータの抽出方法

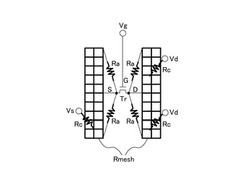

【課題】高精度で実用的なシミュレーションを可能にする拡散抵抗モデルと、これを用いたパラメータ抽出方法とを提供することを目的とする。

【解決手段】パラメータ抽出方法は、マスクレイアウト情報から解析対象となるトランジスタのソース/ドレインの拡散抵抗を、ソース側およびドレイン側のそれぞれにおいて少なくともゲート幅方向に複数個配置された抵抗で構成されたメッシュ状の抵抗回路網の形で抽出するステップ(a)と、ソース側およびドレイン側のメッシュ状の抵抗回路網と、メッシュ状の抵抗回路網の各々におけるゲート幅方向の中央に位置する端子に接続された第1のトランジスタとを含む拡散層抵抗モデルを用いて拡散抵抗のパラメータ抽出を行うステップ(b)とを備えている。また、拡散層抵抗モデルに含まれるトランジスタ数は、ゲート幅方向に配置された抵抗の数より少ない。

(もっと読む)

成膜形状シミュレーション方法及び電子デバイスの製造方法

【課題】膜厚の正確な予測が可能な成膜形状シミュレーション及びこれを用いた電子デバイスの製造方法を提供する。

【解決手段】基体の表面に堆積種を供給することにより形成される薄膜の厚みを計算する成膜形状シミュレーション方法であって、計算に用いるパラメータを、堆積された薄膜の厚みに応じて変更することを特徴とする成膜形状シミュレーション方法が提供される。また、本発明の他の一態様によれば、上記の成膜形状シミュレーション方法により薄膜の堆積条件を求め、前記求められた条件により薄膜を堆積することを特徴とする電子デバイスの製造方法が提供される。

(もっと読む)

マスクデータ補正方法とマスクデータ補正装置及び記録媒体

【課題】短時間で補正の必要な全てのパターンについて一連のプロセスを通したプロセス変換差を求め、光近接効果を補正したマスクデータを作成できるマスクデータ生成方法を提供する。

【解決手段】マスクデータ補正方法において、設計パターンから複数のプロセスステップA1、A2、A3、…Anをへてウェハ上にパターンを作成する際に、各プロセスステップ毎に生ずる変換差△A1、△A2、△A3、…△Anについて、各プロセスステップ毎に補正を行う。そして、各プロセスステップ毎の補正結果に基づいて、ウェハ上で所望のパターンを得られるようなマスクパターンを作成する。

(もっと読む)

イオン注入シミュレーション方法、イオン注入シミュレータ、及びイオン注入シミュレーションプログラム

【課題】ゼロ度のチルト角を用いた高エネルギーイオン注入により半導体基板中に形成された砒素濃度プロファイルを解析モデル(Dual−ピアソン関数)を用いて高精度に予測する。

【解決手段】不純物濃度プロファイルのランダム成分を表す第1のピアソン関数の投影飛程と分散、及び重み付け係数は、現実の不純物濃度プロファイルの最大濃度部31の形状に基づいて抽出される。不純物濃度プロファイルのチャネリング成分を表す第2のピアソン関数の投影飛程と分散は、第1のピアソン関数の投影飛程及び分散を特定の割合で小さくすることで算出される。同一不純物が異なる注入エネルギーで注入された場合、投影飛程と分散は注入エネルギーの減少につれて減少する条件下で抽出され、歪度と尖度、及び重み付け係数は注入エネルギーの減少につれて増加する条件下で抽出される。歪度と尖度は現実の不純物濃度プロファイルのテール部32の形状に基づいて抽出される。

(もっと読む)

シミュレータ、シミュレーションシステムおよびプログラム

【課題】基板処理装置のソフトウェアの品質を向上させる。

【解決手段】基板処理装置のソフトウェアをデバッグする環境として、シミュレーションシステム1を用いる。シミュレーションシステム1には、シミュレータ10とコンピュータ40とを設ける。コンピュータ40には、基板処理装置のソフトウェア(試験対象のソフトウェア)をインストールし、これを動作させることにより基板処理装置の制御ユニットを模擬させる。シミュレータ10においても専用のソフトウェアを動作させることによりコンピュータ40からの制御に従って、基板処理装置の実装処理ユニットの動作を模擬させる。

(もっと読む)

デバイス製造支援装置、そのシミュレーション方法、デバイス製造装置

【課題】本発明は、製造プロセスをシミュレーションすることで、デバイス製造のための最適のパラメータを決定するデバイス製造支援装置を提供することを目的とする。

【解決手段】

製造プロセスを模擬するプロセスシミュレータで形状ばらつきを持った形状モデルを作成し、その結果をデバイスシミュレータに入力する。そして、デバイスの特性ばらつきを評価し、パラメータの最適値と許容範囲を推定し、そのパラメータで再度シミュレータを行なう。これを繰り返してパラメータの最適値と許容範囲を決定するデバイス製造支援装置である。

(もっと読む)

集積回路のプロファイルベースのシミュレーション情報の作成方法

【課題】本発明は、デザインと製作プロセスの決定の影響に関する集積回路(IC)シミュレーション情報の生成法と生成システムを含む。

【解決手段】集積回路用プロファイルベースのシミュレーションデータストアの作成方法であって、構造のプロファイル形状と限界寸法を備えるプロファイルデータを含む入力パラメータの選択されたセットを使用して1つまたは2つ以上のデバイスのシミュレーションを行って、デバイスのデバイス属性を生成し350、光学的計測シミュレータを使用してプロファイルデータに基づいてシミュレーションによる回折信号を生成し、プロファイルデータ及び対応するシミュレーションによる回折信号、1つまたは2つ以上の実行されたシミュレーションを示すシミュレーションタイプ、及びデバイス属性を、対応付けて含むシミュレーションデータストアインスタンスを作成する360。

(もっと読む)

不良確率の算出方法、パターン作成方法及び半導体装置の製造方法

【課題】 不良確率を定量的且つ効果的に求めることが可能な不良確率の算出方法等を提供する。

【解決手段】 設計パターンに基づいて基板上にパターンを形成するためのプロセスで生じるプロセスばらつきを含んだ複数のプロセス条件を想定する工程S32と、プロセス条件それぞれの出現確率を求める工程S32と、設計パターンに基づいて基板上に形成されるパターンを予想するためのプロセスシミュレーションをプロセス条件毎に行う工程S33と、プロセスシミュレーションによって予想されたパターンが所定の基準を満たしているか否かをプロセス条件毎に判定する工程S34と、所定の基準を満たしていないと判定されたパターンのプロセスシミュレーションに用いられたプロセス条件の出現確率どうしを足し合わせるS35工程とを備える。

(もっと読む)

シミュレーション装置およびそれを含んだ検査装置

【課題】多層配線構造の半導体チップの研磨後標高分布を容易に算出することが可能なシミュレーション装置を提供すること。

【解決手段】凸部占有率算出部22は、シミュレーション対象層の直下のマスクデータに基づいてシミュレーション対象層の膜厚を算出し、下層の標高とシミュレーション対象の膜厚とに基づいて凸部占有率を算出する。標高分布算出部23は、プレストン式を用いて、下層の標高と凸部占有率算出部22によって算出された凸部占有率とに基づいてシミュレーション対象層の研磨後の標高を算出する。したがって、多層配線構造の半導体チップの研磨後標高分布を容易に算出することが可能となる。

(もっと読む)

41 - 50 / 113

[ Back to top ]