国際特許分類[H01L21/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847)

国際特許分類[H01L21/00]の下位に属する分類

半導体装置またはその部品の製造または処理 (125,986)

半導体装置以外の固体装置またはその部品の製造または処理であって,グループ31/00〜51/00に分類されている一つの型の装置に特に適していないもの (1)

製造または処理中の試験または測定 (6,126)

製造または処理中の半導体または電気的固体装置の取扱いに特に適用される装置;半導体または電気的固体装置もしくは構成部品の製造または処理中のウエハの取扱いに特に適用される装置 (11,346)

1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275)

国際特許分類[H01L21/00]に分類される特許

81 - 90 / 113

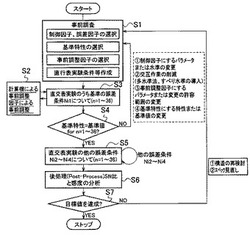

最適化方法、最適化システム、及び、装置を製造する方法

【課題】 複数の特性値がトレードオフの関係を有していても構造因子の最適化が可能な最適化方法を提供する。

【解決手段】 複数の構造因子に複数の目標特性値が依存する一続きの系について構造因子から選択した複数の制御因子に複数の水準を設定し、水準を直交させて選択した複数の実験の組を設定し、トレードオフの関係にある目標特性値を基準特性値として選択し、基準特性値の系において満たすべき基準値を設定し、基準特性値を増減可能な構造因子を事前調整因子として選択し(S1)、基準特性値が実質的に基準値になるように実験の組毎に対応する系の事前調整因子の調整値を計算機を用いて決定し(S2)、調整値と実験の組毎に対応する系の目標特性値を複数の実験特性値として求め(S5)、実験の組と実験特性値に基づいて目標特性値の最適値と最適値を与える水準の組を最適の組として求める(S7)。

(もっと読む)

不純物拡散シミュレーション方法、不純物拡散シミュレーション装置、及び、不純物拡散シミュレーションプログラム

【課題】 広い範囲の製造条件下での正確な不純物拡散シミュレーションを容易に行うことができる方法、装置、プログラムを提供する。

【解決手段】 半導体基板中のイオン注入直後の不純物原子の濃度分布を演算し、当該演算された注入直後の不純物濃度分布の最大濃度に基づいて、イオン注入された1つの不純物原子により半導体基板中に生成される格子間原子の数を設定する。続いて、演算された注入直後の不純物濃度分布と、格子間原子の発生数とに基づいて、半導体基板中に生成された格子間原子の濃度分布を演算し、演算された注入直後の不純物濃度分布と前記格子間原子の濃度分布とに基づいて、熱処理後の不純物原子の濃度分布を演算する。

上記1つの不純物原子により生成される格子間原子の数は、上記最大濃度が予め設定された特定の閾値以上である場合には、不純物原子種に応じて、当該最大濃度のみに依存して一義的に定まる値が設定される。

(もっと読む)

半導体プロセスシミュレーション装置および半導体プロセスシミュレーション方法

【課題】 2次元半導体プロセスシミュレーションにおいて、特定のシミュレーション領域を指定することで、その指定された領域については、3次元シミュレーションと同様の効果が得られるような半導体プロセスシミュレーション装置および半導体プロセスシミュレーション方法を提供することにある。

【解決手段】 半導体素子の2次元構造情報の一部についてシミュレーション領域を指定する領域指定手段と、前記領域指定手段により指定されたシミュレーション領域について3次元製造プロセスの効果を有するプロセス条件を指定する擬似3次元製造プロセス条件指定部とを有するようにしたので、これまで2次元シミュレーションでは取り扱うことのできなかった、3次元構造に起因する形状変化をシミュレーションすることを可能にできる。

(もっと読む)

不純物濃度分布の計算方法

【課題】 解析領域内における不純物濃度分布の計算方法に於いて計算量を削減すること。

【解決手段】 補助節点設定手順2は、解析節点を含み不純物の注入方向に直角な平面に所定の間隔で補助メッシュを設定し、該補助メッシュの交点を補助節点とし、補助節点無効手順2は、解析接点を中心とし、不純物の注入方向に直角な平面上に於ける所定の円外の補助節点を無効補助節点とし、層構造探索手順4は、無効補助節点を除く有効補助節点に基づいて、該有効補助節点の注入方向における層構造の探索を行い、寄与度算出手順5は、有効補助節点の注入方向における位置と、探索された層構造と、有効補助節点から解析節点までの水平方向の位置に基づいて、有効補助節点の不純物濃度分布による解析節点に対する寄与度を求め、濃度分布算出手順6は、解析節点に対する寄与度を前記有効補助節点の全てについて加算する。

(もっと読む)

回路シミュレーション方法

【課題】トランジスタの電気的特性を精度よく再現できる半導体集積回路のシミュレーション方法を提供する。

【解決手段】半導体集積回路のシミュレーション方法は、TEGに搭載した実デバイスの測定値を用いて実デバイスのDC特性とAC特性を再現する回路情報を抽出し、抽出した回路情報をネットリストに反映するステップと、回路シミュレーションを行うステップとを含んでいる。設計寸法と実仕上がり寸法の誤差に起因する回路シミュレーション誤差を低減できる。

(もっと読む)

パラメータ抽出方法およびパラメータ抽出プログラム

【課題】複数の測定値を再現するシミュレーションに使用されるモデルにおいて、前記モデルに含まれる複数のパラメータを抽出するパラメータ抽出方法を提供する。

【解決手段】パラメータ抽出方法は、誤差ベクトルと、一次勾配行列と、対角二次勾配行列を求める勾配生成工程と、誤差ベクトルと一次勾配行列に基づいて、パラメータを求めるパラメータ生成工程と、対角二次勾配行列に基づいて、一次勾配行列を補正する勾配補正工程と、パラメータ生成工程で求めたパラメータによるモデルに基づくシミュレーションにより、複数のシミュレーション値を得るシミュレーション工程とを有し、パラメータ生成工程と勾配補正工程とを繰り返す第一ループにより、シミュレーション工程に与えるパラメータを決定し、勾配生成工程と、第一ループと、シミュレーション工程とを繰り返す第二ループにより、シミュレーション値を複数の測定値に収束させることを特徴とする。

(もっと読む)

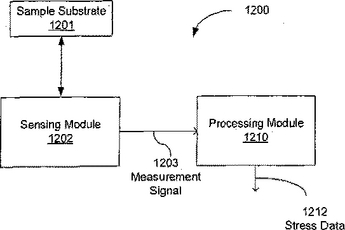

基板に集積した埋込み配線およびバイアのストレス解析および監視

埋込み配線フィーチャを有する層にストレス解析計算を適用してストレス情報を取得し、微細構造を設計し、そして生産プロセスを設計、管理するための技法およびシステム。  (もっと読む)

(もっと読む)

半導体エッチング処理の力学的モデル化及び手法最適化のための方法およびシステム

半導体製造におけるエッチング処理の力学的モデルを生成するための方法およびシステムが開示される。一つの実施形態では、方法は、半導体製造に使用されるエッチング処理をモデル化して、力学的処理モデルを生成する段階を含む。力学的処理モデルは、モデルで予測された出力値が要求される出力値に適合するまで入力値を調整することにより、処理手法の最適化に使用される。  (もっと読む)

(もっと読む)

半導体装置の製造方法、製造装置、シミュレーション方法、及びシミュレータ

【課題】 半導体装置製造プロセスを、テストピースなしに、所望の工程通り又は修正しながら進行することを可能とする半導体装置の製造方法を提供すること。

【解決手段】 複数の工程からなる半導体装置の製造方法において、前記複数の工程の少なくとも1つにおける実観測データを得る工程と、abinitio分子動力学プロセスシミュレータ又は経験的ポテンシャルを与えた分子動力学ミュレータにより、前記複数の工程の少なくとも1つにおける予測データを得る工程と、前記予測データと実観測データとを逐次、実時間で比較検定する工程と、前記比較検定により、製造工程因子の設定値と、前記実観測データから推測される前記複数の製造工程因子との間に有意差が認められた場合、前記製造工程因子を逐次実時間で修正処理する工程とを具備することを特徴とする。

(もっと読む)

半導体記憶装置の製造方法及び半導体設計装置

【課題】 設計の容易化、または設計期間の短縮を実現可能な半導体記憶装置の製造方法及び半導体設計装置を提供する。

【解決手段】 例えば、設計したメモリアレーを検証する際に、様々な分布を備えた各種パラメータVN(ΔVBDL),VN(ΔVTN),VN(IJ)の関数によって定式化されるメモリセルの読み出し信号量VS_EFFを用い、この読み出し信号量VS_EFFの値を各種パラメータ毎の分布からランダムに抽出した値を用いて算出し、この算出結果からメモリセルの良否判定を行い、これらの読み出し信号量VS_EFFの値の算出およびメモリセルの良否判定をメモリアレーが備える多数のメモリセルに対して行う。そして、これによって得られた不良ビットの総数などを、メモリアレーの評価基準に用いる。

(もっと読む)

81 - 90 / 113

[ Back to top ]