国際特許分類[H01L21/20]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 基板上への半導体材料の析出,例.エピタキシャル成長 (11,073)

国際特許分類[H01L21/20]の下位に属する分類

物理的析出を用いるもの,例.真空蒸着,スパッタリング (536)

固体を析出させるガス状化合物の還元または分解を用いるもの,すなわち化学的析出を用いるもの (7,439)

液相成長を用いるもの (330)

国際特許分類[H01L21/20]に分類される特許

81 - 90 / 2,768

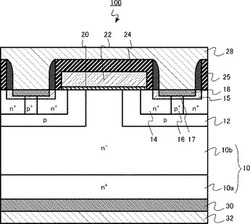

半導体装置および半導体装置の製造方法

【課題】ソース領域に3C−SiC構造のSiCを用いて低い寄生抵抗を実現し、高い性能を備える半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、第1のn型炭化珪素層と、第1のn型炭化珪素層よりもn型不物濃度の低い第2のn型炭化珪素層を有する半導体基板と、第2のn型炭化珪素層に形成される第1のp型不純物領域と、第2のn型炭化珪素層に形成される4H−SiC構造の第1のn型不純物領域と、第2のn型炭化珪素層に形成され、第1のn型不純物領域よりも深さの浅い3C−SiC構造の第2のn型不純物領域と、第2のn型炭化珪素層、第1のp型不純物領域、第1のn型不純物領域の表面にまたがるゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、第1のn型不純物領域上に形成され、底面部と側面部を備え、少なくとも側面部で第1のn型不純物領域との間に第2のn型不純物領域を挟む金属シリサイド層と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

薄膜検査装置及び方法

【課題】

エリプソメトリの技法を用いて結晶状態を迅速に判定することを可能にする。

【解決手段】

表面に多結晶シリコン薄膜が形成された試料を一方向に連続的に移動させながら試料に照明光を照射し、照明光が照射された試料からの反射光をs偏光成分とp偏光成分とに分離し、分離したs偏光の一部を偏光状態を変化させてp偏光を生成し、偏光状態を変化させて生成したp偏光と反射光から分離したp偏光の一部とを合成して合成光を作成し、作成した合成光を検出して第一の信号を得、反射光から分離したp偏光のうち一部を除いた残りのp偏光を検出して第二の信号を得、第一の信号と第二の信号とを処理して得た情報に基づいて試料の表面に形成された多結晶シリコン薄膜の結晶の状態を判定するようにした。

(もっと読む)

窒化物系化合物半導体結晶及びその製造方法並びにIII族窒化物半導体デバイス用基板

【課題】GaN結晶インゴットを含む窒化物系化合物半導体結晶から自立基板を切り出す際のクラックの発生を抑制した窒化物系化合物半導体結晶及びその製造方法並びにIII族窒化物半導体デバイス用基板を提供する。

【解決手段】窒化物系化合物半導体結晶としてのGaN結晶インゴット100は、厚さ方向に沿って外周領域100aとその内側の中心領域100bとを有し、外周領域100aの厚さ方向に垂直な面(Ga極性のc面101)の転位密度の最大値が、中心領域100bの厚さ方向に垂直な面(Ga極性のc面101)の転位密度の最小値の2.0倍以上20倍以下となる転位密度分布を有する。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置

【課題】薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置を提供する。

【解決手段】基板と、前記基板上に位置し、結晶化誘起金属を用いて結晶化された多結晶シリコン層からなり、ソース/ドレイン領域及びチャネル領域を含む半導体層と、前記半導体層上に位置するゲート絶縁膜と、前記ゲート絶縁膜上に位置するゲート電極と、前記ゲート電極上に位置する層間絶縁膜と、前記層間絶縁膜上に位置し、前記半導体層のソース/ドレイン領域と電気的に接続されるソース/ドレイン電極を含み、前記半導体層は前記半導体層の両端部に位置する第1ゲッタリングサイト及び前記第1ゲッタリングサイトと離隔されて前記半導体層のドレイン領域のみに位置する第2ゲッタリングサイトを含むことを特徴とする薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置を提供する。

(もっと読む)

半導体装置、電気光学装置、電力変換装置及び電子機器

【課題】素子特性の低下を抑制することが可能な半導体装置を提供する。

【解決手段】シリコン基板11と、シリコン基板11の表面に形成された炭化シリコン膜12と、炭化シリコン膜12の表面に形成された、開口部13hを有するマスク材13と、開口部13hにおいて露出した炭化シリコン膜12を基点としてエピタキシャル成長された、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14と、単結晶炭化シリコン膜14の表面に形成された半導体素子20と、を含み、マスク材13の上には、単結晶炭化シリコン膜14が会合して形成された会合部12Sbが存在しており、半導体素子20はボディコンタクト領域21を有しており、ボディコンタクト領域21は、シリコン基板11の表面と直交する方向から見て会合部12Sbと重なる位置に配置されている。

(もっと読む)

半導体基材およびその製造方法

【課題】簡便な方法で、結晶化部分を有する半導体基材を得る。

【解決手段】ベース基材と;該ベース基材上に配置された、アモルファス半導体材料由来の結晶性半導体層とを少なくとも含む半導体基材。結晶性半導体層の表面近傍において、SIMSによりGeが検出可能である。

(もっと読む)

薄膜製造方法、それを用いた半導体デバイスの製造方法およびそれらに用いられる半導体薄膜部品

【課題】高品質な半導体薄膜を製造する薄膜製造方法を提供する。

【解決手段】薄膜製造方法は、a−Si膜等の半導体薄膜を第1の基板上に堆積する工程S1と、第1の基板をエッチングして第1の基板と半導体薄膜との間に中空部を形成する工程S2と、半導体薄膜に第2の基板を接触させる工程S3と、半導体薄膜に第2の基板を押し付け、または半導体薄膜が溶融する強度を有するレーザ光を半導体薄膜に照射する工程S4と、第1の基板を半導体薄膜から引き離す工程S5とを備える。

(もっと読む)

半導体膜蒸着装置および半導体膜蒸着方法

【課題】半導体膜の表面欠陥の発生を抑制する半導体膜蒸着装置および半導体膜蒸着方法を提供する。

【解決手段】

半導体原料を収容するるつぼ2と、るつぼ2と対向して基板5を支持する基板支持器6と、るつぼ2と基板5との間でるつぼ2の開口を覆って配置されるマスク4と、るつぼ2およびマスク4を加熱する加熱器3と、るつぼ2、基板支持器6、およびマスク4を収容する真空チャンバ7とを備える半導体膜蒸着装置。るつぼ2から飛散した半導体分子はマスク4内部を衝突しながら通過することで基板5上に表面欠陥が抑制された状態で成膜される。

(もっと読む)

81 - 90 / 2,768

[ Back to top ]