国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

1,061 - 1,070 / 6,199

表示装置およびその製造方法

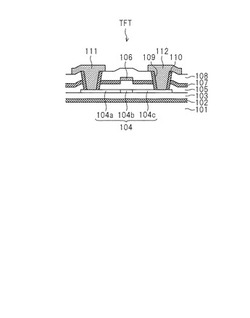

【課題】ゲート絶縁層内に拡散する汚染元素によってトランジスタ特性が低下するのを防止した薄膜トランジスタを有する表示装置、および、その製造方法を提供することを目的とする。

【解決手段】基板101の上側に積層された半導体層104と、半導体層104の上側に積層されるゲート電極106と半導体層104とゲート電極106との間に積層されるゲート絶縁層105と、ソース電極112およびドレイン電極111と、を含む薄膜トランジスタを有する表示装置であって、ソース電極112およびドレイン電極111の少なくとも一方は、ゲート絶縁層105の上側に形成されて、ゲート絶縁層105に形成されるコンタクトホール109を介して半導体層に接続され、コンタクトホール109の側壁には、窒素化合物を含む側壁膜110が形成される、ことを特徴とする表示装置。

(もっと読む)

積層膜の形成方法

【課題】 各膜の組成が異なる積層膜を、極めて効率よく、しかも酸化等の不都合が生じることなく形成することができる積層膜の形成方法を提供すること。

【解決手段】 処理室内に基板1を配置し、処理室に、少なくとも、金属カルボニルを含有する原料を含む成膜原料を導入し、CVDにより基板1上に金属カルボニル中の金属を含む複数の膜6a、6bを含む積層膜を形成する積層膜の形成方法であって、上記積層膜に含まれる膜は、同一処理室内で、原料種および/または成膜条件を異ならせて連続成膜され、上記膜の組成が異なる積層膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置の製造装置

【課題】希釈された溶液を用いて、貴金属を含む被処理膜等を迅速に且つ効果的にエッチングでき、且つ、設備の稼働率を向上できるようにする。

【解決手段】薬液を調合する薬液調合槽24と、調合された薬液を貯蔵する薬液貯蔵槽28と、貯蔵された薬液を用いて半導体基板を処理する処理チャンバ21とを有する半導体装置の製造装置を用いた半導体装置の製造方法は、薬液調合槽24において、酸化剤と錯化剤とを混合して第1の薬液を調合し、薬液調合槽24において、第1の薬液を活性化する。続いて、薬液貯蔵槽28において、活性化された第1の薬液と純水とを混合し、第1の薬液の濃度及び温度を調整することにより、第1の薬液を希釈した第2の薬液を調整する。続いて、処理チャンバ21に投入された半導体基板に第2の薬液を供給する。

(もっと読む)

半導体装置の製造方法

【課題】被覆性及び付着力が高い金属膜を、半導体基板上に低コストで形成できる半導体装置の製造方法を提供する。

【解決手段】Pdイオンを含むPd活性化液28(塩化パラジウム)にGaAs基板16(半導体基板)を浸漬してGaAs基板の表面にPdキャタリスト30を付着させる。このPdキャタリストとGaAs基板が反応してPd−Ga−Asの混合層40が形成される。次に、表面にPdキャタリストが付着されたGaAs基板をPd無電解めっき液42に浸漬してGaAs基板上にPdめっき膜44を形成する。

(もっと読む)

エッチング方法

【課題】エッチング液に含まれるインジウムイオン及びスズイオンの内、特にインジウムイオンの濃度を適切な濃度に維持することができるエッチング方法を提供する。

【解決手段】蓚酸を含むエッチング液Lが貯留された貯留槽11からノズル体16,17にエッチング液Lを供給して吐出させ、酸化インジウムスズ膜が形成された基板Kをエッチングするとともに、ノズル体16,17から吐出されたエッチング液Lを貯留槽11内に回収するエッチング工程と、貯留槽11内に貯留されたエッチング液Lをキレート剤が充填された吸着容器32,33内に通液させて、エッチングによりエッチング液Lに含まれるようになったインジウムイオン及びスズイオンを吸着,除去した後、貯留槽11内に還流させる金属除去工程とを含むエッチング方法において、貯留槽11内に貯留されるエッチング液Lのインジウムイオンの濃度を260ppm以下に維持する。

(もっと読む)

p型有機薄膜トランジスタ、p型有機薄膜トランジスタの製造方法、および、塗布溶液

【課題】電荷注入効率の高いp型有機薄膜トランジスタ、および、金属酸化物を電荷注入層として用いても、金属酸化物が溶解することで電極剥離を起こすことのないp型有機薄膜トランジスタの製造方法、ならびに、この製造方法に用いる塗布溶液を提供する。

【解決手段】p型有機薄膜トランジスタ10Aは、絶縁基板11上に設けられたゲート電極12と、ゲート電極12を被覆して設けられたゲート絶縁層13と、ゲート絶縁層13上に設けられたソース電極14aおよびドレイン電極14bと、ソース電極14aおよびドレイン電極14bの表面に設けられた金属酸化物層15と、ゲート絶縁層13上、かつ金属酸化物層15が形成されたソース電極14aとドレイン電極14bとの間に設けられたp型有機半導体層16と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写技術を使用したパターニングの加工性の向上を図る。

【解決手段】ゲート電極MGを形成するための被加工膜8上にCVD法でカーボン膜9aを形成し、続いてSOG膜を形成する。カーボン膜9aをリソグラフィ技術によるレジストパターンでハーフエッチするとともに、幅寸法をWaから半分のWbにスリミングして芯材パターン部9bを形成する。全面にアモルファスシリコン膜14を形成し、エッチバック処理でスペーサパターン14aを形成し、これをマスクとして芯材パターン部9bと共にカーボン膜9aをエッチングしてマスクパターン9を形成する。レジストを芯材パターンとして用いないので高温で加工ができ、加工性が向上する。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】1メモリセルが6トランジスタを有するSRAMにおいて、コンタクトの微細化をするとリークの発生を回避できる半導体記憶装置及びその製造方法を提供する。

【解決手段】1メモリセルが第1及び第2ドライバトランジスタ(DTr1、DTr2)、第1及び第2転送トランジスタ(TTr1,TTr2)並びに第1及び第2ロードトランジスタ(LTR1,LTr2)の6トランジスタを有するSRAMにおいて第1ドライバトランジスタと第2ドライバトランジスタのソースドレイン領域に基準電位を印加するための接地コンタクトCgと、第1ロードトランジスタと第2ロードトランジスタのソースドレイン領域に電源電位を印加するための電源電位コンタクトCcの径が、共通コンタクトCsを除く他のコンタクト(Cb,Cn,Cw)の径より大きく形成された構成とする。

(もっと読む)

1,061 - 1,070 / 6,199

[ Back to top ]