国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

141 - 150 / 6,199

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電気特性の安定した半導体装置を提供する。とくに、酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜と接して形成されたソース電極、及びドレイン電極と、を有し、ゲート絶縁膜は、少なくとも酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された酸素放出型の酸化膜と、により構成され、酸素放出型の酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

半導体装置の製造方法

【課題】一定のドレイン電圧及びゲート電圧に対して得られるドレイン電流を増大することの出来る半導体装置の製造方法を提供する。

【解決手段】チャンネル領域と、ソース領域及びドレイン領域と、前記ソース領域及びドレイン領域にそれぞれ電気的に接続する合計二つの第1の電極と、前記チャンネル領域上にゲート絶縁膜を介して設けられた第2の電極とを備えた半導体装置の製造に際し、前記ゲート絶縁膜を、酸素の含有量を1ppb以下にした水素添加超純水にIPAを添加した洗浄液を用いて、酸素含有量1ppb以下の窒素雰囲気でしかも遮光した状態で表面の洗浄を行ない、かつ等方性酸化または窒化で形成することにより、前記チャンネル領域と前記ゲート絶縁膜との界面の平坦度を、前記ソース領域から前記ドレイン領域に向かう方向での長さ2nmにおけるピーク・トゥ・バレイ値が0.3nm以下となるようにするとともに、前記第1の電極から前記チャンネル領域までの抵抗率を4Ω・μm以下とした。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

抵抗変化型不揮発記憶装置、半導体装置及び抵抗変化型不揮発記憶装置の製造方法

【課題】安定したスイッチング動作を低コストで実行する抵抗変化型不揮発性記憶装置を提供する。

【解決手段】抵抗変化型不揮発性記憶装置は、第1配線3と、第1配線3上に形成された層間絶縁層53と、層間絶縁膜53上に形成された第2配線6と、第1配線3と第2配線6との間に形成された抵抗変化型素子11とを具備する。層間絶縁層53は、第1配線3と第2配線6とに挟まれるように形成され、第1配線3の幅以下の幅を有するホール9を備える。抵抗変化型素子11は、第1配線3と接して、ホール9の底部に形成された下部電極13と、下部電極13上に形成された抵抗変化層12と、抵抗変化層12上に形成された上部電極11とを備える。下部電極13、抵抗変化層12及び上部電極11は、ホール9の内部に形成される。第1配線3は銅を含み、下部電極13、13aはルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含んでいる。

(もっと読む)

半導体発光装置及びその製造方法

【課題】高いオーミック性と反射率を併せ有する電極構造を備える、低駆動電圧で駆動し、良好な光取り出し効率を有する半導体発光装置及びその製造方法を提供すること。

【解決手段】n型半導体層と、p型半導体層と、前記n型半導体層と前記p型半導体層との間に設けられた活性層と、前記n型半導体層に接して設けられたn電極と、前記p型半導体層に接して設けられたp電極とを具備する半導体発光素子。前記p電極が前記p型半導体層上に少なくとも一部が網目状に形成されたNiO層と、このNiO層に接して形成されたAg層とを含む。

(もっと読む)

導電性膜及びその製造方法並びに導電性膜形成用銀合金スパッタリングターゲット及びその製造方法

【課題】 低抵抗かつ高反射率の特性と共に表面粗さが小さく、高い耐硫化性及び耐塩化性を兼ね備えた導電性膜およびその製造方法を提供すること。

【解決手段】 導電性膜が、Cu:0.1〜2.5原子%、Sb:0.1〜1.5原子%、Ga:0.5〜3原子%を含有し、残部がAgおよび不可避不純物からなる成分組成を有した銀合金で構成されている。この導電性膜は、表面に有機EL素子の透明導電膜が積層され、さらにその上に有機EL層を含む電界発光層が積層される有機EL素子用の反射電極膜として好適である。

(もっと読む)

酸化物半導体層、半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであって、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極との接触抵抗を下げることができる。

(もっと読む)

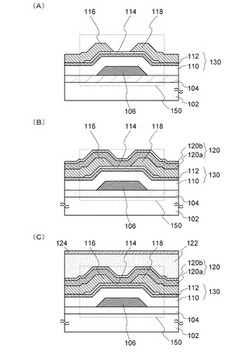

窒化物半導体装置

【課題】ドレイン配線電極に起因する電流コラプス現象への影響が抑制され、且つ耐圧が向上された窒化物半導体装置を提供する。

【解決手段】窒化物半導体からなるデバイス層と、デバイス層上に互いに離間して配置されたソース電極及びドレイン電極と、ソース電極とドレイン電極間でデバイス層上に配置されたゲート電極と、デバイス層上に配置された層間絶縁膜と、ドレイン電極とゲート電極間において層間絶縁膜を介してデバイス層と対向して配置され、ドレイン電極と電気的に接続されたドレイン配線電極と、ゲート電極とドレイン電極間においてデバイス層上に層間絶縁膜を介してデバイス層と対向して配置されたドレイン電極に比べて低電位側のフィールドプレートとを備え、ドレイン配線電極下方の層間絶縁膜の膜厚が、フィールドプレート下方の層間絶縁膜の膜厚よりも厚い。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

141 - 150 / 6,199

[ Back to top ]