国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

161 - 170 / 6,199

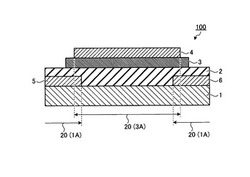

有機半導体素子用電極及びその製造方法

【課題】電界効果移動度が高い有機半導体素子の製造に有用な有機半導体素子用電極、及び、該有機半導体素子用電極を有する有機半導体素子を安価に提供する。

【解決手段】基板1、ゲート電極4、ゲート絶縁膜3、有機半導体層2、ソース電極5及びドレイン電極6を有する有機半導体素子100であって、前記ゲート絶縁膜上に設けられた自己組織化単分子膜のパターン領域と、前記自己組織化単分子膜のパターン領域外である電極形成領域20に設けられたグラフェンナノリボンを含有する薄膜からなる前記ソース電極及びドレイン電極とを有する、有機半導体素子。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体素子の製造方法

【課題】炭化シリコン基板に接するように、オーミック電極となるシリサイド層を形成するに際して、炭化シリコン基板由来の炭素が、オーミック電極内に拡散して表面に析出するのが抑えられ、オーミック電極の上に電極層を密着性良く形成することができる半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明の半導体素子の製造方法は、炭化シリコン基板2のオーミック電極形成領域2aにシリコン層を形成する第1工程と、シリコン層2上に金属層8を形成する第2工程と、熱処理を行うことによって、シリコン層2に含まれるSiと金属層8の構成元素とを反応させ炭化シリコン基板2と接するシリサイド層41を形成する第3工程と、Siと反応せずに残存した金属層8を除去することによって、シリサイド層41を露出させる第4工程とによってオーミック電極4を形成する。

(もっと読む)

半導体素子及びその製造方法

【課題】 この実施の形態は、SiC半導体基板上に形成されたn型半導体領域とp型半導体領域を形成した半導体装置において、n型半導体領域とp型半導体領域の両領域にまたがって、単一の金属電極用いて同時コンタクトを形成することを目的としている。

【解決手段】 この実施の形態の半導体装置は、導電性材料を用いた第1の電極240に、導電型がp型の第1の炭化珪素(SiC)半導体部220と、導電型がn型の第2のSiC半導体部230とが接続され、前記第1の電極と前記第1の界面部において炭素(C)の面密度がピークになるようしている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SiC基板を用いて形成され、金属シリサイド膜と金属電極との密着性の向上する半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、炭化珪素と、炭化珪素上に形成され、第1の層、第1の層よりも低い炭素比率を有する第2の層を備える金属シリサイドと、金属シリサイド上に形成される金属電極を備え、第2の層が第1の層上に形成され、第2の層が金属電極に接し、第2の層中の金属シリサイドの平均粒径が、第1の層中の金属シリサイドの平均粒径よりも大きい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ソース領域に3C−SiC構造のSiCを用いて低い寄生抵抗を実現し、高い性能を備える半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、第1のn型炭化珪素層と、第1のn型炭化珪素層よりもn型不物濃度の低い第2のn型炭化珪素層を有する半導体基板と、第2のn型炭化珪素層に形成される第1のp型不純物領域と、第2のn型炭化珪素層に形成される4H−SiC構造の第1のn型不純物領域と、第2のn型炭化珪素層に形成され、第1のn型不純物領域よりも深さの浅い3C−SiC構造の第2のn型不純物領域と、第2のn型炭化珪素層、第1のp型不純物領域、第1のn型不純物領域の表面にまたがるゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、第1のn型不純物領域上に形成され、底面部と側面部を備え、少なくとも側面部で第1のn型不純物領域との間に第2のn型不純物領域を挟む金属シリサイド層と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

配線の形成方法

【課題】基板上に不要な配線を形成させず、かつ少ない工程数で、基板上に配線を形成する方法を提供すること。

【解決手段】基板にフォトレジストを塗布、露光、パターニングをした後、配線となる導電層を形成し、基板上のフォトレジストを除去する方法で、基板上の第1、第2及び第3の領域には単位面積あたり第1、第2及び第3の累積露光量で、かつ第2の累積露光量は、第1の累積露光量よりも大きく、第3の累積露光量よりも小さくなるように露光し、パターニングによって、第3の領域においてフォトレジストが全て除去された露出面が、第2の領域において第2の上面を有するフォトレジスト層が、第1の領域において第2の上面より高い第1の上面を有するフォトレジスト層が形成され、第1の上面の基板上への投影は、露出面の投影と重なる部分と、第2の上面の投影と重なる部分とを有し、導電層は第3の領域を含む範囲において形成される。

(もっと読む)

半導体装置

【課題】低オン抵抗であって、かつ、ノーマリーオフの電界効果型トランジスタを提供する。

【解決手段】基板10の上に形成された電子走行層11と、電子走行層11の上に、電子走行層11よりもバンドギャップの広い半導体により形成された電子供給層12と、電子供給層12の上に、電子供給層よりもバンドギャップの狭い半導体により形成されたバリア形成層13と、バリア形成層13の上に、不純物のドープされた半導体により形成された上部チャネル層14と、バリア形成層13及び上部チャネル層14を除去することにより形成されたバリア形成層13及び上部チャネル層14の側面と、側面に形成された絶縁膜20と、絶縁膜20を介し形成されたゲート電極21と、上部チャネル層14と接続されるソース電極22と、電子供給層12または電子走行層11と接続されるドレイン電極23と、を有する。

(もっと読む)

ニッケル膜の成膜方法

【課題】CVDにより不純物の少ないニッケル膜を高スループットで成膜することができるニッケル膜の成膜方法を提供すること。

【解決手段】基板上に、成膜原料として、分子構造中に窒素−炭素結合をもつ配位子を有し、配位子中の窒素がニッケルに配位した構造を有するニッケル含有化合物を用い、還元ガスとして、アンモニア、ヒドラジン、およびこれらの誘導体から選択された少なくとも1種を用いたCVDにより初期ニッケル膜を成膜する第1工程と、初期ニッケル膜の上に、成膜原料として、分子構造中に窒素−炭素結合をもつ配位子を有し、配位子中の窒素がニッケルに配位した構造を有するニッケル含有化合物を用い、還元ガスとして水素ガスを用いたCVDにより主ニッケル膜を成膜する第2工程とを有する。

(もっと読む)

161 - 170 / 6,199

[ Back to top ]