国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

181 - 190 / 6,199

半導体装置

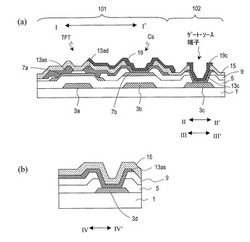

【課題】端子部のコンタクトホールのテーパー形状を高い精度で制御する。

【解決手段】酸化物半導体層7a、ソース配線13as、ドレイン電極13adを備えた薄膜トランジスタと、第1接続部3c、第2接続部13cおよび第2接続部上に形成された第3接続部19cを備えた端子部とからなる薄膜トランジスタである。第2接続部は、第1および第2絶縁膜5,9に設けられた第1開口部内で第1接続部と接し、第3接続部19cは、保護膜に設けられた第2開口部内で第2接続部と接する。第1開口部は、第1絶縁膜5および第2絶縁膜9を同時にエッチングすることによって形成、第2開口部は、保護膜15を前記第1および第2絶縁膜とは別個にエッチングすることによって形成される。第2接続部13cは、第1開口部における第1および第2絶縁膜の端面を覆い、かつ、第2開口部における保護膜15の端面を覆っていない。

(もっと読む)

パターン形成装置、パターン形成方法及びパターン形成基板の製造方法

【課題】ビアホール、コンタクトホール、スルーホール等の穴部の内面のみを改質して、穴部に導体を形成する。

【解決手段】基板100には、上面100aの開口から下面100bの開口に向かうにつれて直径が増加しているビアホール110が設けられている。基板100の下面には、表面に微小な凹凸形状が形成された光反射用基板46が配置される。照射部40からビアホール110にレーザ光Lが照射されると、ビアホール110の開口部から入射したレーザ光は、基板100の下面に配置された光反射用基板46の表面によって散乱反射される。このレーザ光Lの反射光は、ビアホール110の内面110aに照射され、内面110aが表面改質される。

(もっと読む)

銅膜作製方法

【課題】下地層との密着性に優れた銅膜を製造する方法の提供。

【解決手段】成膜対象物上に下地層としてチタン膜を形成した後、この下地層を水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理し、次いでその上に銅膜を作製する。このように銅膜を作製した後、さらに水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理を行う。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に接続するソース電極層またはドレイン電極層との接触抵抗の低減を図る。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層のうち、酸化物半導体層と接する一層104a、104bを薄いインジウム層または薄いインジウム合金層とする。なお、酸化物半導体層103は、インジウムを含む。二層目以降のソース電極層105aまたはドレイン電極層105bの材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

ハフニウム系薄膜形成方法およびハフニウム系薄膜形成材料

【課題】常温で液体であり、そして安定性に富んでおり、原料の安定供給が行え、高品質なハフニウム系薄膜を安定して形成できる技術を提供する。

【解決手段】下記の一般式[I]で表される化合物であるハフニウム系薄膜形成材料。

一般式[I]

LHf(NR1R2)3

(但し、Lは置換シクロペンタジエニル基、R1,R2はアルキル基であり、R1とR2とは互いに異なっていても同じであってもよい。)

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かす、適切な構成を備えた保護回路等を提供する。

【解決手段】ゲート電極101を被覆するゲート絶縁層102と、ゲート絶縁層102上においてゲート電極101と重畳する第1酸化物半導体層103と、第1酸化物半導体層103上においてゲート電極と端部が重畳し、導電層105aと第2酸化物半導体層104aが積層された一対の第1配線層38及び第2配線層39とを有する非線形素子170aを用いて保護回路を構成する。ゲート絶縁層102上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子170aの特性を向上させることができる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

電子装置

【課題】カーボンによるバンドギャップ・エンジニアリングを可能とし、カーボン原子に基づく多彩なエレクトロニクスを達成して、信頼性の高い電子装置を実現する。

【解決手段】電子装置は、単層のグラフェン膜1と、グラフェン膜1上の両端に設けられた一対の電極2,3とを有しており、グラフェン膜1では、電極2,3間の領域において、中央部位のBC間が複数のアンチドット10が形成されてなる第1の領域1aとされており、第1の領域1aの両側におけるAB間及びCD間がアンチドットの形成されていない第2の領域1bとされている。

(もっと読む)

ナノギャップ電極及びその製造方法

【課題】導電性膜を作製してから、導電性膜に通電しナノギャップを作製するプロセスを行うことなく、エレクトロマイグレーション時の大幅な印加電流の低減とプロセス時間の短縮することができるナノギャップ電極の製造方法を提供する。

【解決手段】絶縁体基板70上に金属電極80,81を形成し、この金属電極間にエレクトロマイグレーションを誘発する電圧又は電流を印加しながら、絶縁体基板上に導電性材料を堆積して、ナノスケールのギャップを有する導電性細線を形成する。

(もっと読む)

オーミック電極とその形成方法

【課題】コンタクトホールを形成するために用いられたレジスト膜を、硫酸を含むエッチング液を利用して除去することが可能なオーミック電極の形成方法を提供する。

【解決手段】積層電極部2を形成する積層電極部形成工程と、積層電極部2を熱処理するアニール工程と、熱処理後の積層電極部2を被覆部3で被覆して被覆電極部4を形成する被覆電極部形成工程と、被覆電極部4を覆うように半導体層1の表面に絶縁体膜5を形成する絶縁体膜形成工程と、被覆電極部4に対応して開口7が形成されているレジスト膜6を絶縁体膜5の表面にパターニングするレジスト膜形成工程と、レジスト膜6の開口7から露出する絶縁体膜5を除去して被覆電極部4を露出させる露出工程と、硫酸を含むエッチング液を用いてレジスト膜6を除去するレジスト膜除去工程を備えている。被覆部3の材料は、金又は白金である。

(もっと読む)

181 - 190 / 6,199

[ Back to top ]