国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

231 - 240 / 6,199

アモルファスシリコン膜の成膜方法および成膜装置

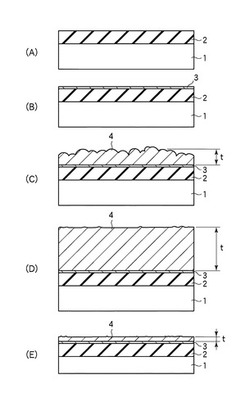

【課題】 より平滑な表面を持ち、かつ、更なる薄膜化を達成することが可能なアモルファスシリコン膜の成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを供給し、下地2表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2表面のシード層3にアミノ基を含まないシラン系ガスを供給し、シード層3上にアモルファスシリコン膜4を、層成長する厚さに形成する工程と、層成長する厚さに形成されたアモルファスシリコン膜4をエッチングし、該アモルファスシリコン膜4の膜厚tを減ずる工程とを備える。

(もっと読む)

導電膜パターンの形成方法

【課題】信頼性の高い導電膜パターンの製造方法を提供する。

【解決手段】本発明に係る導電膜パターンの製造方法は、基板10上に導電膜21を成膜し、導電膜21の表面に対して他の層を積層する前に、酸素をプラズマ化したプラズマアッシング処理を施し、表面処理した導電膜21上に、当該導電膜21をパターン形成するためのマスクパターン30を形成する。次いで、マスクパターン30を用いて導電膜21をウェットエッチングによりパターン形成する。基板10は、半導体基板であることが好ましい。導電膜パターンは、例えば、配線、電極パッド等である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを十分に抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された化合物半導体積層構造2と、化合物半導体積層構造2上方に形成されたゲート電極3、及び平面視でゲート電極3を間に挟む2個のオーミック電極4a及び4bと、が設けられている。更に、ゲート電極3上方に形成され、ゲート電極3並びにオーミック電極4a及び4bから絶縁分離されたフィールドプレート6が設けられている。フィールドプレート6のオーミック電極4a及び4bを互いに結ぶ方向における少なくとも一方の端部は、平面視で、オーミック電極4a及び4bとゲート電極3との間に位置する。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

炭化珪素半導体装置

【課題】少ない工程数で形成でき、耐熱性に優れた温度検出素子を備える炭化珪素(SiC)半導体装置を提供する。

【解決手段】SiC半導体装置は、SiC基板1に形成された半導体素子と、底面にバリアメタル14を備える配線層を用いて形成したソース電極15およびゲートパッド16と、その配線層のバリアメタル14の一部を用いて形成した測温抵抗体20を備える。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の十分な低減を可能とする半導体装置の製造方法を提供する。

【解決手段】半導体装置1の製造方法は、少なくとも一方の主面を含む領域が単結晶炭化珪素からなる基板を準備する工程と、一方の主面上に活性層23を形成する工程と、基板の前記一方の主面とは反対側の他方の主面を含む領域を研削する工程と、他方の主面を含む領域を研削する工程において形成されたダメージ層22Cを除去する工程と、ダメージ層22Cが除去されることにより露出した主面に接触するように裏面電極を形成する工程とを備え、一方の主面は{0001}面に対するオフ角が50°以上65°以下となっている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

窒化物系半導体素子

【課題】本実施形態は、窒化物半導体層のクラックがほとんどなく、表面の粗度が極めて優秀であるので、全体的な安定性の向上された窒化物系半導体素子を提供する。

【解決手段】本実施形態の窒化物系半導体素子は、基板と、前記基板上に形成されるアルミニウムシリコンカーバイド(AlSixC1−x)前処理層と、前記前処理層上に形成されるAlがドーピングされたGaN層と、前記AlがドーピングされたGaN層上に形成されるAlGaN層とを含む。

(もっと読む)

半導体基板製品の製造方法、これに用いられる薄膜除去液

【課題】白金(Pt)化合物の薄膜を、他の部材を過度に酸化・腐食することなしに除去する半導体基板製品の製造方法、これに用いられる薄膜除去液を提供する。

【解決手段】白金化合物の薄膜を有する半導体基板を準備する工程と、薄膜除去液を準備する工程と、前記半導体基板に前記薄膜除去液を適用して前記白金化合物の薄膜を除去する工程とを含む半導体基板製品の製造方法であって、前記薄膜除去液が、ハロゲン分子、ハロゲンイオン、及び水を組み合わせて含む半導体基板製品の製造方法。

(もっと読む)

231 - 240 / 6,199

[ Back to top ]