国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

5,121 - 5,130 / 6,199

配線パターン形成方法、デバイスの製造方法、非接触型カード媒体の製造方法、電気光学装置の製造方法及びアクティブマトリクス基板の製造方法

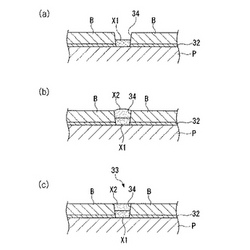

【課題】複数の材料を積層してパターンを形成することによって、一種類の材料では得られなかった機能性をパターンに付与する。

【解決手段】機能液を基板上に配置させてパターンを形成する方法であって、上記基板P上に上記パターンの形成領域に応じたバンクBを形成する工程と、上記バンク間34に第1の機能液X1を配置する工程と、配置された上記第1の機能液X1上に第2の機能液X2を配置する工程と、上記バンク間に積層した上記第1の機能液X1と上記第2の機能液X2とに対して所定の処理を施すことによって複数の材料が積層されてなる上記パターン33を形成する工程とを有する。

(もっと読む)

導電性厚膜組成物、電極、およびそれから形成される半導体デバイス

【課題】新規なAg/Al包含組成物および半導体デバイスの提供。

【解決手段】(a)(1)Al、Cu、Au、Ag、PdおよびPt;(2)Al、Cu、Au、Ag、PdおよびPtの合金;および(3)それらの混合物から選択される導電性金属粒子と、(b)Pbフリーであるガラスフリットと、(c)有機媒体とを含み、成分(a)および(b)が成分(c)中に分散されており、該導電性金属粒子の平均直径が0.5〜10.0μmの範囲内である導電性厚膜組成物、および該組成物から形成される電極ならびに該電極を含む半導体デバイス(例えば、太陽電池)。

(もっと読む)

エッチング方法及び電子デバイスの製造方法

【課題】 タンタルを含む材料と、窒化珪素とのエッチング選択比を容易に制御可能としたエッチング方法及びこれを用いた電子デバイスの製造方法を提供する。

【解決手段】 タンタルを含む材料からなる第1の部分と、窒化珪素からなる第2の部分と、を有する被処理体をエッチングするエッチング方法であって、エッチングガスに窒素を添加した第1の混合ガスを用いて前記第2の部分をドライエッチングすることを特徴とするエッチング方法を提供する。

(もっと読む)

有機エレクトロルミネッセンス素子及びその製造方法

【課題】素子の高効率化およびコンパクト化が可能な,有機エレクトロルミネッセンス素子及びその製造方法を提供する。

【解決手段】基板300上に半導体層310,ゲート電極330及びソース/ドレイン電極350,355を含む薄膜トランジスタ,及びソース/ドレイン電極350,355と接続される第1の電極360を同一層に形成し,第1の電極360上に積層され,少なくとも有機発光層を有する有機膜層380と,有機膜層380上に積層される第2の電極390とを含み,ソース/ドレイン電極及び第1の電極は,透明導電膜と,透明導電膜の下部に,0.1〜0.3原子%のSm,0.1〜0.5原子%のTb,0.1〜0.4原子%のAu及び0.4〜1.0原子%のCuを含むAg合金で形成される反射膜とを含んで形成される有機エレクトロルミネッセンス素子が提供される。

(もっと読む)

電界効果トランジスタおよびエピタキシャル基板

【課題】二次元正孔ガスの電気伝導を避けることができる構造を有しておりWruzite構造の窒化物系材料から成る電界効果トランジスタを提供する。

【解決手段】AlN支持基体13は、Wruzite構造を有する結晶からなり、導電性或いは絶縁性の支持体である。AlNエピタキシャル層15は、AlN支持基体13のN面エリア上に設けられている。GaNエピタキシャル層17は、AlNエピタキシャル層15上に設けられている。ゲート電極19は、GaNエピタキシャル層17上に設けられており、該GaNエピタキシャル層17にショットキ接合する。ゲート電極19は、二次元電子ガス23の伝導を制御する。ソース電極25およびドレイン電極27には、該ゲート電極19によって制御される電流が流れる。ヘテロ接合21の界面に二次元正孔ガスが形成されることなく、電界効果トランジスタ11の伝導が二次元電子ガス23を介して提供される。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、過電圧から素子を保護するために設けられた保護ダイオードの耐圧特性が向上しないという問題があった。

【解決手段】本発明の半導体装置では、基板2上のエピタキシャル層3には、素子保護用の保護ダイオード1が構成されている。エピタキシャル層3表面にはショットキーバリア用金属層14が形成され、ショットキーバリア用金属層14の端部20の下方にはP型の拡散層9が形成されている。そして、P型の拡散層9よりカソード領域側にフローティング状態のP型の拡散層10、11が形成され、アノード電位が印加された金属層18と容量結合している。この構造により、空乏層の大きな曲率変化を低減し、保護ダイオード1の耐圧特性を向上させている。

(もっと読む)

半導体装置およびその製造方法

【課題】 電極層の電気的特性の悪化を抑制できるようにする。

【解決手段】 ゲート電極分離領域GVに形成された第1の多結晶シリコン層5を除去する工程の前に、ゲート電極形成領域GCに形成されたシリコン窒化膜10、WSi膜9、第3の多結晶シリコン層8、ONO膜7、第2の多結晶シリコン層6の側壁を保護するための保護膜14を形成しているため、これらの各層6〜10を保護することができ第1の多結晶シリコン層5をエッチング処理するときの各層6〜10の機能低下を抑制できる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 良好な電気的特性のトランジスタが得られるようにし、これによって半導体装置の微細化や高密度化を可能にし、さらには3次元に積み重ねることをも可能にした、半導体装置の製造方法とこの製造方法によって得られる半導体装置を提供する。

【解決手段】 基体1上に形成された結晶性半導体膜3のうち第1の部分以外の少なくとも第2の部分及び第3の部分に不純物を注入する第1の工程と、第2の部分および第3の部分にそれぞれソース及びドレインを形成する第2の工程とを備える。第2の工程において、少なくとも第2の部分および第3の部分に対して加熱処理を施すことにより、第1の部分の少なくとも一部をシードとする第2の部分及び第3の部分の固相エピタキシー過程を誘起する。

(もっと読む)

半導体装置

【課題】 LOCOSオフセット構造を採らなくても、トランジスタの耐圧が高い半導体装置の提供を提供する。

【解決手段】 MOSトランジスタ100のゲート電極11とドレインプラグ17との間のシリコン基板1上に、絶縁膜7を介して電界集中緩和用のスポットプラグ19が設けられており、このスポットプラグ19は、ゲート電極21の上方まで延ばされたソース電極21に接続している。このような構成であれば、ゲート電極11下とドレイン領域5との境界部分は、スポットプラグの影響を受けて電界集中が緩和され、その勾配が緩やかになる。

(もっと読む)

固相エピタキシー方式を用いた半導体素子及びその製造方法

【課題】コンタクト物質で低温熱工程によりエピタキシャルシリコンを形成しながらも、エピタキシャルシリコンの有する高い自らの比抵抗値によるコンタクト抵抗の増加を防止できるエピタキシャルシリコンをコンタクトとする半導体素子及びその製造方法を提供する。

【解決手段】固相エピタキシー工程を用いたエピタキシャル層と、前記エピタキシャル層上の第1金属層と、前記第1金属層上の窒化物系バリヤメタルと、前記バリヤメタル上の第2金属層と、前記エピタキシャル層と第1金属層との間に形成された金属シリサイドとを含む。

(もっと読む)

5,121 - 5,130 / 6,199

[ Back to top ]