国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

5,161 - 5,170 / 6,199

半導体装置及びその製造方法

【課題】キャパシタを配置する構造においてキャパシタ絶縁膜や上部電極界面に与えられたダメージを効率よく回復させる半導体装置及びその製造方法を提供すること。

【解決手段】本発明の一形態の半導体装置は、半導体基板(101)の上方に形成された、下部電極(115)とMOx型導電性酸化物(Mは金属元素、Oは酸素元素、x>0)を含む電極膜を有する上部電極(117)とで誘電体膜(116)を挟んでなるキャパシタと、前記上部電極に接続されたコンタクト(122)と、を備え、前記電極膜は、前記コンタクト直下の膜厚がその他の部分の膜厚に比べて薄い。

(もっと読む)

バリヤメタル層及びその形成方法

【課題】 銅の配線材料に対して有効なバリヤメタル層を提供する。

【解決手段】 シリコン層或いはシリコンを含むシリコン含有層64と銅層68,70との間に介在されてシリコンの吸い上げを防止するためのバリヤメタル層において、前記バリヤメタル層としてTiSiN膜66を用いる。これにより、銅の配線材料に対して有効なバリヤメタル層とする。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】 エミッタサイズを縮小でき、且つ製造コストを低減することができるHBTを実現する。

【解決手段】 高濃度n型の第1サブコレクタ層102上に、バンドギャップの小さい材料からなる高濃度n型の第2サブコレクタ層108と、i型又は低濃度n型のコレクタ層103と、高濃度p型のベース層104と、バンドギャップの大きい材料からなるn型のエミッタ層105と、高濃度n型のエミッタキャップ層106と、バンドギャップの小さい材料からなる高濃度n型のエミッタコンタクト層107とが順次形成されている。エミッタコンタクト層107からは、エミッタ電極を兼ねる配線115Aが引き出され、エミッタ層105からは、ベース電極を兼ねる配線115Bが引き出され、第2サブコレクタ層108からは、コレクタ電極を兼ねる配線115Cが引き出されている。

(もっと読む)

半導体装置の製造方法

【課題】 様々なパターンを有するゲート電極をフルシリサイド化することができる半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板10上にゲート絶縁膜30を形成し、ゲート絶縁膜上にゲート電極40、42を形成し、ゲート電極上に金属膜100を堆積し、第1の熱処理を施すことによってゲート電極の上部をシリサイド化し、第1の熱処理においてシリサイド化しなかった金属膜を除去し、第2の熱処理を施すことによってゲート電極の下部までシリサイド化する。

(もっと読む)

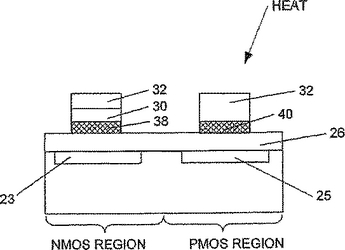

デュアルメタルゲート電極を有するCMOSデバイスの製造方法

金属エッチング工程においてゲート誘電体(26)が露出することを防止するために、処理の間、メタルゲート(30)とゲート誘電体(26)との間の超薄窒化アルミニウム(AlNx)バッファ層(28)を使用する、デュアルメタルゲートCMOS構造

を構築する方法。不必要なゲートメタルをエッチング除去した後、CMOS構造は熱処理される。熱処理の間に、メタルゲート(30)との反応を通じてバッファ層(28)は完全に消費され、新らしいメタル合金(38,40)が形成される。その結果、実効酸化膜厚は最小限しか増加しない。バッファ層(28)およびゲートメタル(30)は、元のゲートメタルの仕事関数が熱処理工程の結果変化するため、メタル/誘電体界面の仕事関数の決定に重要な役割を果たす。  (もっと読む)

(もっと読む)

非SiO2ゲート誘電体を有するMOSデバイスの製造方法

多結晶シリコン層(20)がゲート誘電体(10)上に堆積され、次いでその一部分が再酸化されて、当該ポリSi層と下側のゲート誘電体との間に酸化物(30)の薄層を形成するようにする。続いて、ポリSi層が完全シリサイド化形態(50)に変換され、FUSIゲートを生成させる。ゲート誘電体は、例えばHf含有材料であるhigh−k材料、又はSiON、或いは別の非SiO2誘電体とすることができる。障壁酸化物層(30)は、好ましくは1nm未満の厚みである。 (もっと読む)

半導体装置の製造方法

【課題】 銅配線のEM耐性とSM耐性を、ともに向上させる。

【解決手段】 不純物を含む銅めっき膜をシリコン基板1の上に成膜した後、銅めっき膜を結晶成長させて、複数の銅結晶粒とそれらの粒界に分布する不純物層とで構成された第一銅膜9cを形成する。次に、第一銅膜9cより不純物濃度が高い第二銅膜10を第一銅膜9cの上に形成し、第二銅膜10に含まれる不純物を第一銅膜9cに拡散させて、第一銅膜9cの結晶粒界に偏析する不純物濃度を高める。

このように形成することにより、第一銅膜9cの結晶粒の粒径は十分に大きくなる。これにより、結晶粒界における拡散パスを減少させ、EM耐性を向上させることができる。また、第一銅膜9cに発生するボイドの移動を抑え、SM耐性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】

半導体ウェハ1枚当たりから得られるチップ収量が改善された半導体装置の製造方法を提供する。

【解決手段】

本発明の半導体装置の製造方法は、シリコン基板10周縁の略帯状の第1領域34を除く第2領域35において、シリコン基板10の表面領域にシリサイド層12を形成する工程と、

シリコン基板10全面に絶縁膜14を形成する工程と、

絶縁膜14上にレジスト膜15を形成し、次いでレジスト膜15を露光工程により開口してパターンを形成する工程と、

前記パターンが形成されたレジスト膜15をマスクとして、絶縁膜14を選択的にエッチングする工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の少なくともゲート絶縁膜側をハフニウムと窒素とを含む膜で形成し、そのハフニウムと窒素とを含む膜中の窒素を適性な組成比にすることで、従来から用いられているPoly−Si電極とほぼ同レベルの良好な移動度を得ることを実現する。

【解決手段】半導体基板11上にゲート絶縁膜14を介してゲート電極15を備えた電界効果トランジスタからなる半導体装置1であって、前記ゲート電極15は少なくとも前記ゲート絶縁膜14側がハフニウムと窒素とを含む膜からなり、前記ハフニウムと窒素とを含む膜は少なくとも窒素を含みかつハフニウムと窒素とに対する窒素の組成比が51%以下である。

(もっと読む)

ゲート電極積層およびゲート電極積層を用いる方法

【課題】エッチングの容易なポリシリコン−メタル積層で構成されるゲート電極構造を提供する。

【解決手段】少なくとも1層のポリシリコン3と少なくとも1層のポリSi1−xGex材料の層4とを有するゲートコンダクタを備える半導体デバイスの基板上のゲート電極積層構造であり、ポリシリコン3とポリSi1−xGex材料の層4のエッチングにより、終点検出が可能であるため、上記構造を効果的にエッチングすることができる。

(もっと読む)

5,161 - 5,170 / 6,199

[ Back to top ]