国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

5,291 - 5,300 / 6,199

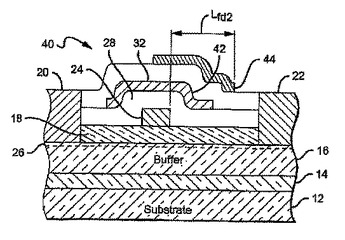

ゲート−ソースフィールドプレートを含むワイドバンドギャップトランジスタ

本発明に係るトランジスタは、チャネル層を有する活性領域を含み、この活性領域と接触してソースおよびドレイン電極が形成され、このソース電極とドレイン電極との間にあって活性領域と接触したゲートが形成される。ゲートとドレイン電極との間およびゲートとソース電極との間の複数の活性領域の表面の少なくとも一部分上にスペーサ層がある。このスペーサ層上にはフィールドプレートがあり、活性領域の上のスペーサ上をドレイン電極に向かって延びる。このフィールドプレートはさらに、活性領域の上のスペーサ層上をソース電極に向かって延びる。少なくとも1つの導電性経路が、フィールドプレートをソース電極またはゲートに電気的に接続する。  (もっと読む)

(もっと読む)

金属膜パターンの形成方法

【課題】 半導体基板の配線若しくはバンプ、又は、磁気ヘッド基板の磁極部等の金属膜パターンを所望のパターンどおりに得ることができる金属膜パターンの形成方法をを提供する。

【解決手段】 基板上に所定のパターンでレジストパターンを形成するレジストパターン形成工程と、この基板の少なくともレジストパターンが形成されている面を、水に対しオゾンが1ppm以上30ppm以下含有されたオゾン水に接触させるオゾン水処理工程と、この基板のレジストが形成された面側に金属をめっきするめっき工程と、この基板からレジストパターンを除去するレジストパターン除去工程とを有する金属膜パターンの形成方法により、上記課題を解決した。

(もっと読む)

マグネトロンスパッタリング装置用高純度Wシリサイド材

【課題】高信頼性の半導体素子を得るために高融点金属、高融点金属からなる合金、高融点金属の珪化物、Ti,Ta,Wシリサイド,Ti−W合金の窒化物からなる膜をコンタクトバリアー層またはゲート電極などに用い、半導体素子のリーク電流を抑える。

【解決手段】ソース−ドレイン領域の接合深さが0.1〜0.3μmである半導体素子のWシリサイドから成るコンタクトバリアー層又はゲート電極層のAl含有量を原子数で1×1016個/cm3以下、W以外の重金属元素の含有量が1×1017個/cm3以下およびアルカリ金属の含有量が3×1016個/cm3以下に形成することが可能であり、Al濃度が1ppm以下であることを特徴とするマグネトロンスパッタリング装置用高純度Wシリサイド材である。

(もっと読む)

半導体装置及びその製造方法

【課題】 フィールドプレート電極を有する高周波特性の良好な半導体装置を提供するとともに、その製造時における歩留まりを向上させた製造方法を得る。

【解決手段】 ゲート電極16とドレイン電極13との間の表面保護膜15上に、ゲート電極16から所定の距離Lgfをおいてフィールドプレート電極17が設け、耐圧特性を向上させるとともに、これら2つの電極間を橋状の配線18により接続し、内部での帰還容量となる動作層12との間の不要な容量等を増加を抑える。また、ゲート電極16とフィールドプレート電極17とを、これら電極間を接続する配線18も含めて同一工程において一体に形成し、ゲート電極16とフィールドプレート電極17との距離Lgfを良好な精度に維持する。さらに、配線18に開口部19を設け、この配線18を容易に橋状に形成可能とする。

(もっと読む)

マグネトロンスパッタリング装置用高純度Ti材の製造方法

【課題】高信頼性の半導体素子を得るために、Ti窒化物から成る膜をコンタクトバリアー層またはゲート電極などに用い、半導体素子のリーク電流を抑える。

【解決手段】ソース−ドレイン領域の接合深さが0.1〜0.3μmである半導体素子のTi窒化物から成るコンタクトバリアー層のAl含有量を原子数で1×1018個/cm3以下に形成するためにTi原料からエレクトロンビ−ム溶解法でAlを3ppm以下に除去することを特徴とするマグネトロンスパッタリング装置用高純度Ti材の製造方法である。

(もっと読む)

半導体装置、LEDヘッド及びそれを用いた画像形成装置

【課題】層間絶縁膜と金属配線層との間に厚さが5〜500〔Å〕のTiから成る密着層を形成する事によって、金属配線層としてのアノード配線層及びカソード配線層と層間絶縁膜とのコンタクト特性が良好となり、アノード配線層及びカソード配線層とを同一の工程で同時に形成する事ができる半導体装置、LEDヘッド及びそれを用いた画像形成装置を提供する。

【解決手段】半導体基板21と、該半導体基板上に形成され、該半導体基板へのコンタクトホールが開口された層間絶縁膜23と、一端が前記コンタクトホールに接続され、他端がボンディングパッドを構成する金属配線層13と、前記層間絶縁膜と金属配線層との間に設けられ、厚さが5〜500〔Å〕のTiから成る密着層31とを有する。

(もっと読む)

有機薄膜トランジスタ及びそれを備えた平板ディスプレイ装置

【課題】有機薄膜トランジスタ及びそれを備えた平板ディスプレイ装置を提供する。

【解決手段】基板と、基板の上部に配置されたゲート電極と、ゲート電極と絶縁されたp型有機半導体層と、ゲート電極と絶縁されて相互離隔されて配置されたソース電極及びドレイン電極と、ソース電極及びドレイン電極とp型有機半導体層との間に介在された正孔注入層と、を備えることを特徴とする有機薄膜トランジスタである。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 NiSiが用いられたシリサイド上ライナー窒化膜のエッチング特性を改善し、コンタクトホール底での過度のエッチングを防止する。

【解決手段】 半導体基板301の素子活性領域にシリサイド層308を形成する工程と、半導体基板上にライナーになるシリコン窒化膜309を形成する工程と、シリコン窒化膜上に層間絶縁膜を形成する工程と、層間絶縁膜にコンタクトホールを形成する工程とを含み、シリコン窒化膜は、原子層蒸着法によりジクロロシランとアンモニアを用いて曝露するサイクルを繰り返すことにより成膜され、成膜段階におけるアンモニアガスの曝露時間は、表面反応が平衡状態になる緩和時間の2〜10倍である。これにより、窒化膜中の塩素濃度を低減でき、Si−N結合が増やすことができるため、ウェットエッチング耐性を向上できる。

(もっと読む)

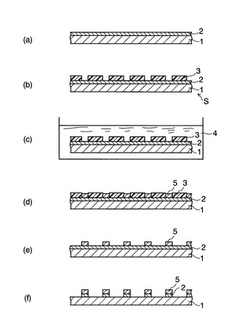

金属、半導体、絶縁体パターンの線幅及びサイズを縮める方法

【課題】既存の方法で先ず線幅やサイズの大きい(例えば、50nm以上)パターン202などを製作した後、物理的、化学的、機械的蝕刻を利用してパターンのサイズを更に縮める。

【解決手段】従来の方法で線幅が20nm以上の所定サイズの線幅を有するパターン202を作るステップS302、及び前記パターン202を物理的、機械的加工で削ってサイズを縮めるステップ、前記パターン202を化学的方法で蝕刻することによって前記パターン202のサイズを縮めるステップ、並びに前記パターン202を材料の最外から分解して前記パターン202のサイズを縮めるステップなどの中から選択された一つのステップS306を含むことにより金属、半導体、絶縁体パターンの線幅及びサイズを縮める。

(もっと読む)

薄膜の積層構造、その形成方法、成膜装置及び記憶媒体

【課題】下地との密着性が高くて膜剥がれの発生を抑制でき、しかも、微細化が進んでもステップカバレジを十分に高くすることができ、更には合金種の元素を十分に拡散させることができる薄膜の積層構造の形成方法を提供する。

【解決手段】真空引き可能になされた処理容器4内で被処理体の表面に複数の薄膜を堆積して薄膜の積層構造を形成する方法において、合金種としての第1の金属を含む原料ガスと還元ガスとを用いて第1の金属よりなる合金種膜104を形成する合金種膜形成工程と、前記第1の金属とは異なる母材としての第2の金属を含む原料ガスと還元ガスとを用いて第2の金属よりなる母材膜106を前記合金種膜よりも厚く形成する母材膜形成工程とを、それぞれ1回以上交互に行うようにする。

(もっと読む)

5,291 - 5,300 / 6,199

[ Back to top ]