国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

6,061 - 6,070 / 6,199

整流素子およびそれを用いた電子回路、並びに整流素子の製造方法

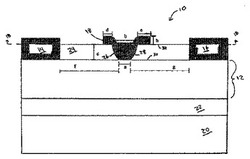

一対の電極と、該一対の電極間に設けられた、1本または複数のカーボンナノチューブにより構成されるキャリア輸送体と、を備え、前記一対の電極のうち、一方の電極および前記キャリア輸送体の第1の界面と、他方の電極および前記キャリア輸送体の第2の界面と、が異なる障壁レベルとなるように、これら2つの接続構成を異なる構成とすることで、高周波応答性、耐熱性に優れたキャリア輸送体を備えた整流素子を提供し、併せて、それを用いた電子回路、並びに整流素子の製造方法を提供する。  (もっと読む)

(もっと読む)

半導体構造、二重仕事関数のCMOSデバイス、二重仕事関数のCMOS回路、および基板上に二重仕事関数のCMOSデバイスを形成する方法(炭化金属ゲート構造および形成方法)

【課題】 炭化金属を含むゲート電極を含む少なくとも1つのFETを含む相補型金属酸化膜半導体(CMOS)などの半導体デバイスおよび形成方法を提供することにある。

【解決手段】 このCMOSは、ある金属とある金属の炭化物によって二重仕事関数が与えられる、二重仕事関数の金属ゲート電極を含む。

(もっと読む)

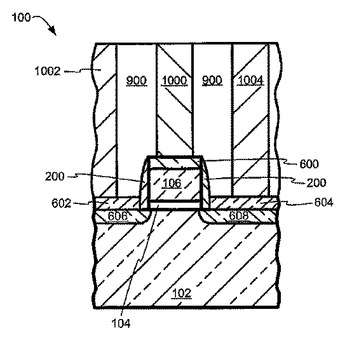

シリサイド成長ドーパント雪かき効果の使用による、デバイス中に階段接合の形成

トランジスタ(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に絶縁層(702)をたい積する。その後、絶縁層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

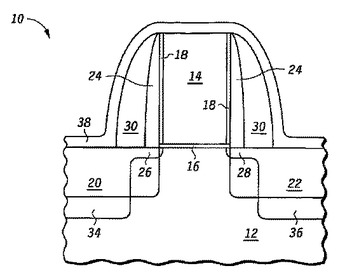

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

窒化ガリウム材料デバイスおよびその形成方法を提供する。該デバイスは、電極規定層を包含する。電極規定層は典型的にはその内部に形成されたビアを有し、該ビア内に電極が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。 (もっと読む)

III族窒化物素子の不動態化およびその方法

【課題】

【解決手段】III族窒化物半導体素子およびその製造方法の実施形態は、高温処理中にIII族窒化物材料に損傷を与えずに、素子のコンタクトを形成することを可能にする低抵抗の不動態化層を備えてよい。不動態化層は、素子全体を不動態化するために用いられてよい。不動態化層は、さらに、素子のコンタクトと活性層との間に設けられて、導電のための低抵抗の電流路を提供してもよい。この不動態化処理は、FET、整流器、ショットキダイオードなど、任意の種類の素子に用いて、破壊電圧を改善すると共に、コンタクトの接合部付近の電界集中効果を防止してよい。不動態化層は、外部拡散に関してIII族窒化物素子に影響を与えない低温アニールで活性化されてよい。

(もっと読む)

電極、その製造方法およびそれを用いた半導体素子

低接触抵抗を実現しつつ表面荒れの少ない電極が得られる技術を提供する。

半導体膜101の上部に設けられる電極であって、この半導体膜101の上部にこの半導体膜の側から順に積層された第一金属層102と第二金属層103とを有し、この第一金属膜102が、Alからなり、この第二金属膜103が、Nb、W、Fe、Hf、Re、TaおよびZrからなる群より選ばれる1種以上の金属からなることを特徴とする電極。

(もっと読む)

モノリシック集積型エンハンスメントモードおよびデプリーションモードFETおよびその製造方法

【課題】 製造コストを低減し品質の均一性および安定性を高めたモノリシック集積型エンハンスメントモード/デプリーションモードFETデバイスを提供する。

【解決手段】 単一の半導体多層構造でデプリーションモード(Dモード)FETをエンハンスメントモード(Eモード)FETとモノリシックに集積回路化する。上記多層構造にはチャネル層を設け、その上に障壁層をオーバーレイし、さらにその上にオームコンタクト層をオーバーレイする。これらDモードFETおよびEモードFETのソースコンタクトおよびドレーンコンタクトをオームコンタクト層に接続する。またDモードFETおよびEモードFETのゲートコンタクトを障壁層に接続する。障壁層の中のEモードゲートコンタクトの下に非晶質化領域を設ける。この非晶質化領域が障壁層との間の埋込みEモードSchottkyコンタクトを構成する。代わりに実施例ではDモードFETのゲートコンタクトを障壁層にオーバーレイした第1の層に接続し、その第1の層の中にDモード非晶質化領域を形成する。

(もっと読む)

シリサイドをソース/ドレインに用いた半導体素子

半導体素子において、非常に深い位置に達するゲルマニウムイオン注入及びゲルマニウムの活性化をニッケルシリサイド形成用のニッケルの堆積の前に行なう。ゲルマニウムを活性化させることにより、イオン注入領域の格子定数が、シリコンであることが好ましい母体基板の格子定数よりも大きくなる。このような変化が加えられた格子によって、ニッケルダイシリサイドの形成を防止することができるという効果が得られる。その結果、ニッケルシリサイドスパイクを防止することができる。  (もっと読む)

(もっと読む)

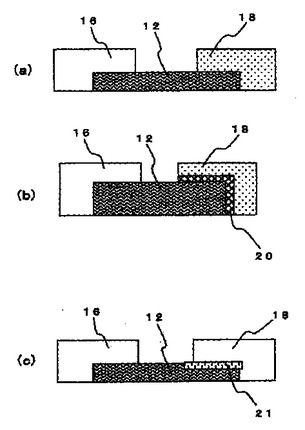

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

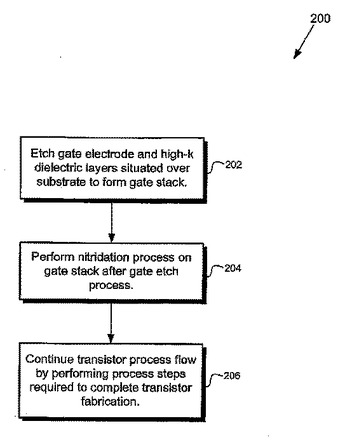

トランジスタ製造プロセスにおいて、high−kゲート絶縁体を組み入れる方法

本発明の例示的な一実施形態は、その上に位置するhigh-k誘電体層と、このhigh-k誘電体層上に位置するゲート電極層と、を含む基板(104)上に電界効果トランジスタを形成する方法である。この方法は、基板(104)上に位置するhigh-k誘電体部(106)と、high-k誘電体部(106)上に位置するゲート電極部とを含むゲートスタック(102)を形成するように、ゲート電極層およびhigh-k誘電体層をエッチングするステップ(202)を含む。この例示的な実施形態によれば、この方法は、ゲートスタック(102)上で窒化プロセスを実行するステップ(204)をさらに含む。この窒化プロセスは、ゲートスタック(102)のサイドウォール(110)を窒化するように、窒素を含むプラズマを利用するステップによって実行することができる。この窒化プロセスの結果、窒素がhigh-k誘電体部(106)に入り込み、窒素がhigh-k誘電体部(106)中に酸素拡散バリアを形成するようにされてよい。  (もっと読む)

(もっと読む)

6,061 - 6,070 / 6,199

[ Back to top ]