国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

6,071 - 6,080 / 6,199

コンタクトの形成中、コンタクトホール幅の増大を防ぐ方法

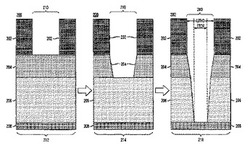

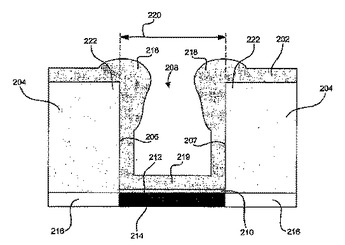

一形態によれば、半導体ダイに位置するシリサイド層(214)上にコンタクトを形成する方法は、コンタクトホール(208)の各側壁(206、207)、及び、コンタクトホール(208)の底部に位置する自然酸化物層(210)に、バリア層(202)を堆積するステップを含み、各側壁(206、207)は、絶縁層(204)のコンタクトホールによって形成される。コンタクトホール(208)の各側壁(206、207)、及び、酸化物層(210)にバリア層(202)を堆積する(150)ステップにおいて、バリア層(202)の厚さを、コンタクトホール(208)の上部が、コンタクトホール(208)の底部よりも厚くなるよう最適化してもよい。この形態によれば、バリア層(202)の一部分(219)及びコンタクトホール(208)の底部に位置する酸化物層(210)を除去し、シリサイド層(214)を露出させるステップを含む方法も提供される。  (もっと読む)

(もっと読む)

FETゲート電極用のCVDタンタル化合物(TaおよびNを含む化合物の化学的気相堆積方法および半導体電界効果デバイス)

【課題】電界効果デバイスのゲート材料を提供すること。

【解決手段】電界効果デバイスのゲート材料として用いられるTaおよびNの化合物であって、さらに別の元素を含む可能性があり、約20mΩcmより小さな比抵抗を有し、約0.9より大きなN対Taの元素比を有する化合物が開示される。そのような化合物の代表的な実施態様であるTaSiNは、誘電体層および高k誘電体層を含むSiO2上の一般的なCMOSプロセス温度で安定であり、n型Siの仕事関数に近い仕事関数を有する。第3アミルイミドトリス(ジメチルアミド)Ta(TAIMATA)などのアルキルイミドトリス(ジアルキルアミド)Ta化学種をTa前駆体として用いる化学的気相堆積方法によって、金属性Ta−N化合物を堆積する。この堆積は共形であり、これらのTa−N金属化合物のCMOSプロセスフローへの融通の利く導入を可能にする。TaNまたはTaSiNを用いて加工されたデバイスは、ほぼ理想的な特性を示す。

(もっと読む)

基板上にパターン化層を形成する方法

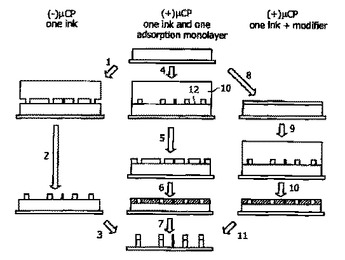

ソフト・リソグラフィのパターン化工程によって基板(24)上にパターン化された自己組織化単分子層(20)を形成する方法であって、その方法は、a)前記パターン化された自己組織化単分子層(20)の必要なパターンを画定するためのパターン化手段(10)を提供すること、b)前記基板(24)の表面(22)上に自己組織化単分子層(20)を形成すること、c)前記パターン化手段(10)を前記基板(24)の前記表面に適用することであって、前記パターン化手段(10)が前記基板表面の選択された領域に修飾剤を送達するように配置され、前記選択された領域が前記必要なパターン又はそのネガに対応し、前記修飾剤が化学物質を含み、且つ前記選択された領域で、前記自己組織化単分子層(10)の分子と前記基板(24)の前記表面との間の相互作用の強さを変えるように配置されること、並びにd)ステップc)の後、その分子と前記基板の前記表面との間でより低い相互作用の強さを示す前記自己組織化単分子層(20)の領域を選択的に除去又は置換し、それによって前記必要なパターンを有する自己組織化単分子層(20)を形成することを含む。修飾剤は、工程の要求に応じて、自己組織化単分子層の分子と基板の最上面との間の相互作用の強さを弱める又は高めるように選択されてもよい。  (もっと読む)

(もっと読む)

部分的シリサイド化シリコン層を有する集積回路

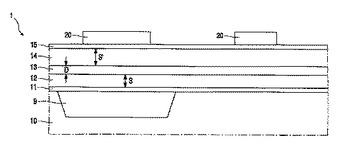

この集積回路(1)は、シリサイド化部(122)及び非シリサイド化部(123)を有する第1のシリコン層(120)を有する抵抗素子などの電気的装置(2)と、例えばキャパシタ、電界効果トランジスタ又は不揮発性メモリゲート堆積部などの他の電気的装置(3)とを有する。他の電気的装置(3)は、誘電層厚さ(D)を有する誘電層(130)を有する。電気的装置(2)の非シリサイド化部(123)は、誘電層厚さ(D)を有する他の誘電層(131)により被覆され、シリサイド化部(122)は、他の誘電層(131)により被覆されない。このような集積回路(1)は、リソグラフィ工程数の少ない本発明による方法によって形成可能となる。

(もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

半導体装置とこの種の半導体装置の製造方法

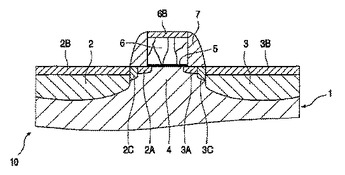

この発明は、基板と半導体本体(1)とを有する半導体装置(10)に関し、半導体本体(1)がソース(2)及びドレイン(3)を有する第一のFET(3)を備え、ソース(2)及びドレイン(3)は、金属シリサイドを含む接続領域(2B,3B)が設けられ、そして、ゲート(6)下部のチャネル領域(4)と境界を成し且つソース(2)及びドレイン(3)より厚みが薄く且つドーピング濃度が低いソース及びドレイン領域拡張部(2A,3A)に接続されている。ソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)とは、第一の導電型で且つ厚み及びドーピング濃度がソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)との間の中間領域(2C,3C)により互いに接続されている。このようにして、接続領域(2B,3B)と基板と間にリーク電流並びに短絡が起きるのが抑制され、一方で、ソース及びドレイン領域拡張部(2A,3A)を用いることの効果が維持される。好ましくは、中間領域(2C,3C)がゲート(6)直近のスペーサ(7)下部に位置し、好ましくは、これらは、なるべく傾けられたイオン注入により形成される。  (もっと読む)

(もっと読む)

半導体デバイスにおける造形部分のパターン形成技術

【課題】 パターン形成される造形部分の微小寸法を縮小する技術を提供すること。

【解決手段】 半導体の処理のための技術が提供される。1つの態様において、半導体デバイスに1つまたはそれ以上の造形部分をパターン形成するための方法は、以下のステップを含む。反射防止材のエッチング中に、1つまたはそれ以上の造形部分の少なくとも1つの微小寸法が縮小される。リソグラフィ構造もまた提供される。

(もっと読む)

等方性エッチングプロセスを使ったショットキーバリアMOSFET製造方法

【課題】電流の流れを調整するトランジスタデバイスの組立て方法において、更なる駆動電流を可能にし、デバイスの動作を最適化するプロセスを提供すること。

【解決手段】本発明の一実施形態における方法は、チャンネル領域に対するショットキーバリア接合位置のより良い制御を与えるために、メタルソースドレイン接触の形成に先行して等方性エッチングプロセスを利用する。このショットキーバリア10接合の配置の制御性からの改善により、更なる駆動電流を可能にし、デバイスの動作を最適化する。

(もっと読む)

シリコン領域に形成されたニッケル/コバルトシリサイド領域を有する半導体デバイス

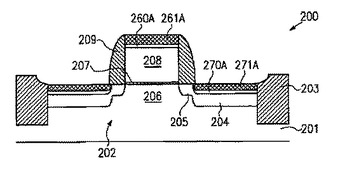

電界効果トランジスタのゲート電極などの、シリコン含有領域に、埋め込まれたニッケルシリサイド層(260A)、続いてコバルトシリサイド層(261A)を形成することによって、縮小されたシリコン回路構造のシート抵抗及び接触抵抗を過度に損なうことなく、デバイスを更に縮小することができるように、両シリサイドの優れた特性が組み合わせられる。  (もっと読む)

(もっと読む)

無定形炭素層を含むマスキング構造

多数層を有するマスキング構造が形成される。そのマスキング構造は、無定形炭素層と該無定形炭素層上に形成されたキャップ層とを含む。無定形炭素層は透明無定形炭素を含む。キャップ層は非酸化物材料を含む。マスキング構造は、半導体装置の製作中、エッチング・プロセスにおけるマスクとして使用可能である。 (もっと読む)

6,071 - 6,080 / 6,199

[ Back to top ]