国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

6,091 - 6,100 / 6,199

金属−炭化珪素オーミックコンタクトの局所的アニーリングおよびそのようにして形成された素子

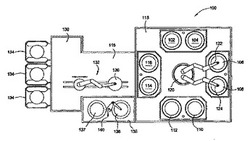

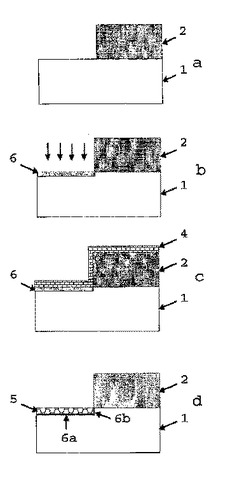

炭化珪素(SiC)基板上に金属を形成し、この金属とSiC基板との界面部をアニーリングして、そこに金属−SiC材を形成し、SiC基板上のある箇所ではアニーリングされないようにして、そこには金属−SiC材が形成されないようにすることによって半導体素子のコンタクトを形成することができる。

(もっと読む)

(もっと読む)

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

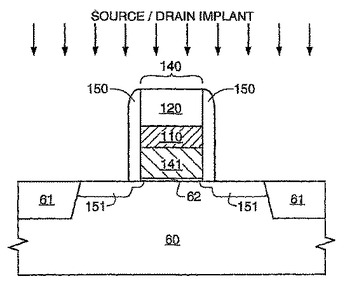

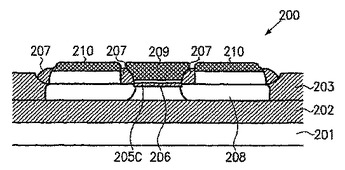

ゲートの枯渇を低減した注入ゲート電極を有する電界効果型トランジスタ、及び、このトランジスタを製造する方法

ドレイン領域及びソース領域(208)を規定する前に、注入マスク(220)を形成することにより、ゲートドーパント密度をドレインドーパント密度及びゲートドーパント密度から効果的に分離する。さらに、注入マスク(220)を除去した後に、ゲート電極(205)の横方向寸法は、十分に確立された側壁スペーサ(207)技術によって規定される。その結果、フォトリソグラフィ及び異方性エッチングに基づく従来の方法に対してデバイスの縮小に関する優位性を提供する。  (もっと読む)

(もっと読む)

接点の製作方法とその接点を持つ電子部品

この発明は、ケイ化物(5)などの第一の層とそれに隣接する層との間に、不活性化した境界面(6a,6b)を製作する方法に関する。この方法の間には、S、Se、Teなどの不活性化元素を、この層構造の中に組み入れるとともに、温度処理の間に、少なくとも第一の層の隣接層との境界面において濃縮させる。こうすることによって、ショットキー障壁を低下させるとともに、遷移域の仕事関数を調節すことに成功した。例えば、ソース接点とドレイン接点の両方又は一方のショットキー障壁が低い又はそれどころか負であるショットキー障壁MOSFETとスピントランジスターの素子を開示している。  (もっと読む)

(もっと読む)

バイポーラ・トランジスタを有する半導体装置の製造方法及びバイポーラ・トランジスタを有する装置

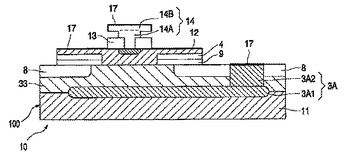

本発明は、バイポーラ・トランジスタ装置(10)の製造に関し、この装置内に、絶縁層(13)内のウィンドウ内に存在し絶縁層(13)を覆って横方向に延びる多結晶シリコン領域(14)を用いて、エミッタが形成される。シリコン領域(14)、並びに、絶縁領域(13)及びシリコン領域(14)のスタックに隣接する別のシリコン領域(12)が、この構造を覆って堆積される金属層(16)によってシリサイド化される。形成されるシリサイド(17)のブリッジを回避する手段がスタックの側面に形成される。本発明によれば、形成されるシリサイドのブリッジを回避するための手段は、シリコン領域(14)の上面とスタックの側面の表面に沿った他のシリコン領域(12)の上面との間の間隔が、絶縁層(13)と半導体層(14)の厚さの合計よりも大きく形成されるように、スタックの側面が構築されることを備える。スタック側面の正又は負の傾斜によって増大された通路によりシリサイドのブリッジが回避される。好ましい実施形態は、スタックの側面がどのように構築されるかに関する。  (もっと読む)

(もっと読む)

有機反射防止膜(ARC)を有する半導体装置及びその方法

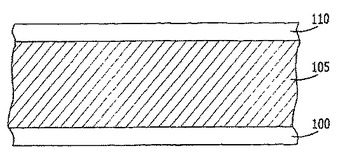

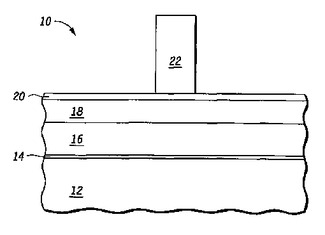

半導体装置(10)の製造において、エッチングされる導電性材料(16)上のパターニング積層部は、下層にあるオルトケイ酸テトラエチル(TEOS)層(20)のパターニングに用いられるパターニングフォトレジスト層(22)を有している。TEOS層(20)は、従来より低い温度で成膜される。低温TEOS層(20)は、有機反射防止膜(ARC)(18)上に設けられ、有機反射防止膜は、導電層(16)上に設けられる。低温TEOS層(20)は、有機ARC(18)とフォトレジスト(22)との間の接着を提供し、低い欠陥性を有し、ハードマスクとして機能し、有機ARC(18)と共に望ましくない反射を低減させる位相シフト層として機能する。  (もっと読む)

(もっと読む)

集積回路におけるコンタクトサイズをサイジングすることによって多層コンタクトを製造するための方法

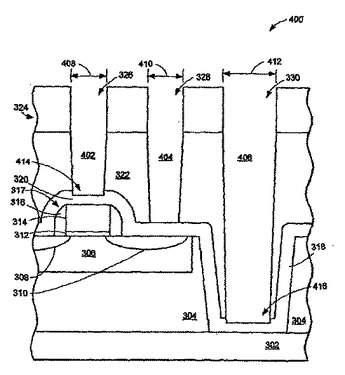

集積回路を形成するための方法(600)は、第1半導体基板(202)上の半導体デバイス(317)表面上の誘電材(322)における第1深さに第1開口部(228)、(338)、(402)をエッチングし、第1半導体基板(202)表面上の誘電材(322)において第2深さに第2開口部(230)、(340)、(404)をエッチングする。第1開口部(228)、(338)、(402)、及び第2開口部(230)、(340)、(404)は、エッチングラグに起因してほぼ同時に第1及び第2深さにエッチングするためにそれぞれ異なってサイズされる。第1開口部(228)、(338)、(402)、及び第2開口部(230)、(340)、(404)は、導電材で充填される。  (もっと読む)

(もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

半導体部品およびその製造方法

本発明は、有機半導体、特に有機電界効果トランジスタ、との静電的相互作用を制御するための層(10)を備える半導体部品に関するものである。上記半導体部品は、上記化合物が、a)基板と結合するために、少なくとも1つのアンカー基(1)を有する化合物を含み、b)当該化合物は、少なくとも1対の自由電子対および/または双極子モーメントを有する少なくとも1つの基(2)をすることを特徴とする。さらに、本発明は、そのような化合物を含む層を形成させるための方法に関するものであり、当該方法によれば、特に、論理関数を付加的に補正(レベルシフト)しなくてもよいOFETを製造することができる。  (もっと読む)

(もっと読む)

バリヤ金属上に直接銅めっきするマルチステップ電着法

本発明の実施形態は、基板表面に、通常はバリヤ層に銅シード層を堆積させる方法を教示している。その方法は、基板表面を銅溶液に入れるステップであって、該銅溶液が錯体形成銅イオンを含んでいる、前記ステップを含んでいる。電流又はバイアスを基板表面に印加し、錯体形成銅イオンを還元してバリヤ層に銅シード層を堆積させる。 (もっと読む)

6,091 - 6,100 / 6,199

[ Back to top ]