国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

6,101 - 6,110 / 6,199

半導体デバイスを製造する方法およびその方法で使用するための装置

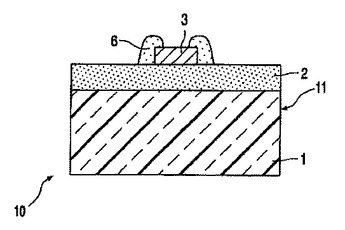

本発明は、基板(1)および少なくとも1つの半導体要素を含んだ半導体本体(11)を有した半導体デバイス(10)の製造方法に関する。その方法では、要素の形成後、少なくとも1つの電気的絶縁層(2)または電気的導体層(3)を含んだ層構造が形成され、開口部が、パターン形成されたフォトレジスト層(4)およびエッチング・プロセスの助けによって層構造中に形成され、残渣が、エッチング・プロセス中に半導体本体(11)の表面上に形成され、エッチング・プロセス後に、フォトレジスト層(4)が、酸素含有化合物を使用する処理によって灰にされ、その後、表面が、酸を水で希釈した溶液を含んだ洗浄剤を、室温より高い温度に加熱して使用する洗浄作業を受け、それによって形成された残渣が除去される。本発明によれば、硫酸が、洗浄剤用の酸として選択される。  (もっと読む)

(もっと読む)

高いfTおよびfmaxを有するバイポーラ・トランジスタおよびこれを製造する方法

【課題】 ベース抵抗を低減したバイポーラ・トランジスタを提供する。

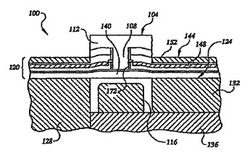

【解決手段】 高いfTおよびfmaxを有するバイポーラ・トランジスタ(100)は、エミッタ(104)、ベース(120)、およびコレクタ(116)を含む。エミッタは、下部(108)と、この下部を越えて延在する上部(112)とを有する。ベースは、真性ベース(140)および外部ベース(144)を含む。真性ベースは、エミッタの下部とコレクタとの間に位置する。外部ベースは、エミッタの下部からエミッタの上部を越えて延在し、エミッタの上部の下からエミッタの上部の下よりも外側まで延在する連続導体(148)を含む。連続導体は、ベース・コンタクト(図示せず)から固有ベースまでの低電気抵抗の経路を提供する。このトランジスタは、第2の導体(152)を含むことができ、これは、エミッタの上部の下に延在せず、これによって、外部ベースを介した電気抵抗を更に低減する。

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

銅メタライゼーションのためのALD窒化タンタルの集積

窒化タンタル/タンタルバリア層を堆積させるための方法および装置が、集積処理ツールでの使用のために提供される。遠隔発生プラズマによる洗浄ステップの後、窒化タンタルは原子層堆積法で堆積され、タンタルはPVDで堆積される。窒化タンタル/タンタルは、堆積された窒化タンタルの下の導電性材料を露呈するために、誘電体層の部材の底部から除去される。場合によって、さらなるタンタル層が、除去ステップの後に物理気相堆積法で堆積されてもよい。場合によって、窒化タンタル堆積およびタンタル堆積は同一の処理チャンバで生じてもよい。シード層が最後に堆積される。 (もっと読む)

バリヤ物質の原子層堆積

1以上の物質層のバリヤ層を原子層堆積により堆積させるために基板を処理する方法が提供される。一態様においては、金属含有化合物の1以上のパルスと窒素含有化合物の1以上のパルスを交互に導入することにより基板表面の少なくとも一部上に金属窒化物バリヤ層を堆積させるステップと、金属含有化合物の1以上のパルスと還元剤の1以上のパルスを交互に導入することにより金属窒化物バリヤ層の少なくとも一部上に金属バリヤ層を堆積させるステップとを含む基板を処理する方法が提供される。金属窒化物バリヤ層及び/又は金属バリヤ層の堆積前に基板表面上で浸漬プロセスが行われてもよい。 (もっと読む)

縦型構造複合半導体装置

複数の縦型構造光学電子装置を結晶基板上に形成し、レーザリフトオフ処理で基板を取り除く工程を含んだ縦型構造光学電子装置の製造方法が開示されている。続いてこの方法は基板の代わりに金属支持構造体を形成する。1例ではこの形成には電気メッキ処理及び/又は無電メッキ処理が利用される。1例では縦型構造体はGaN型であり、結晶基板はサファイヤ製であり、金属支持構造体は銅を含む。本発明の利点には、高性能で生産効率が高い大量生産用の縦型構造LEDの製造が含まれる。 (もっと読む)

半導体処理システムのための前駆物質を生成する方法及び装置

本発明の実施形態は、半導体処理システム(320)の前駆物質を生成する装置に関する。装置は、側壁(402)、上部、底部を有するキャニスタ(300)を含んでいる。キャニスタ(300)は、上の領域(418)と下の領域(434)を有する内容積(438)を画成している。一実施形態においては、装置は、更に、キャニスタ(300)を部分的に取り囲んでいるヒータ(430)を含んでいる。ヒータ(430)によって、上の領域(418)と下の領域(434)間に温度勾配が生じる。また、精製ペンタキス(ジメチルアミド)タンタルから原子層堆積によってバリヤ層、例えば、窒化タンタルバリヤ層を形成する方法も特許請求される。 (もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

デュアルメタルゲートデバイスの形成方法

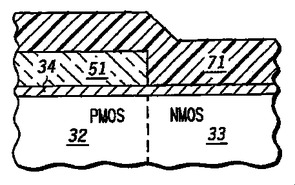

異種金属により形成されるデュアルメタルゲートを備えるMOSトランジスタ(10)を形成する方法を提供する。HfO2のようなゲート誘電体(34)を半導体基板(31)の上に堆積させる。次に、犠牲層(35)をゲート誘電体(34)を覆うように堆積させる。犠牲層(35)をパターニングして、基板(31)の第1領域(32)(例えばpMOS)の上のゲート誘電体(34)が露出し、かつ基板(31)の第2領域(33)(例えばnMOS)の上のゲート誘電体(34)が犠牲層(35)によって保護されたままになるようにする。第1ゲート導体材料(51)を残りの犠牲領域(35)の上に、かつ露出したゲート誘電体(34)の上に堆積させる。基板(31)の第2領域(33)の上の第1ゲート導体材料(51)がエッチングにより全て除去されるように第1ゲート導体材料(51)をパターニングする。第1ゲート導体材料(51)を取り除く際に、第2領域(33)上の犠牲層(35)は、下層の誘電体材料(34)にダメージが加わるのを防止するように機能することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つ高バリア性を有するバリアメタルを提供する。

【解決手段】バリアメタル201 が、配線溝16の底面及び側壁の表面に沿って形成された膜厚16nmのTaN0.87膜31と、TaN0.87膜上に形成され、配線溝16に埋め込み形成されたCuダマシン配線17に接する膜厚4nmのTaN1.19膜32とから構成されている。

(もっと読む)

6,101 - 6,110 / 6,199

[ Back to top ]