国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

6,151 - 6,160 / 6,199

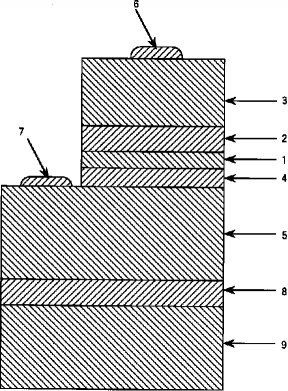

3−5族化合物半導体とその製造方法および発光素子

【課題】 欠陥の少ない高品質の3−5族化合物半導体とその製造方法、及び該化合物半導体を用いた発光特性の良好な発光素子を提供する。

【解決手段】 サファイア基板9の鏡面研磨C面上に基板温度550℃で、トリメチルGaとNH3を供給しGaNのバッファ層8を形成した後、基板温度を1100℃まで上げシランを送りSiをドープしたn型GaN層5を成長させ、さらに同温度でノンドープのGaN層4を形成した。次に基板温度を780℃まで下げ、TEG、TMI,NH3を用いて発光層のIn0.3Ga0.7N層1を成長させ、さらに同温度でTEG,TEA及びNH3を送り保護層のGa0.8Al0.2N層2を形成した後、基板温度を1100℃に上げMgドープしたGaN層3を成長させた。この3−5族半導体試料を炉から取出しN2中熱処理してGaN層3を低抵抗のP型層にした後、P及びn電極6,7を付けて明瞭な青色発光素子が得られた。

(もっと読む)

3−5族化合物半導体とその製造方法および発光素子

半導体装置の製造方法

【課題】 開口パターンの底部及び側壁下部の膜厚が減少し、それにより、ゲート抵抗が増加してしまったり、FETの信頼性が低下してしまう等の課題がある。

【解決手段】 絶縁膜層3上に形成された開口パターン11上に開口パターン11よりも幅の広いレジスト開口パターン12が形成されるように絶縁膜層3上に成膜されたWSi膜5上に逆テーパー形状を有する第2のレジスト膜6を形成する。

(もっと読む)

接続孔を形成する工程を有する配線構造の形成方法

【目的】 接続孔を形成する工程を有する配線構造の形成について、段差のある下地上に形成した層間絶縁膜に深さの異なる接続孔を形成する場合も、オーバーエッチングの問題が生じず、よって特性の良好な配線構造が得られる技術を提供する。

【構成】 半導体装置製造における多層ポリSi配線プロセス等について、SiO2 等から成る段差を有する下地1上に形成した層間絶縁膜3に接続孔5a,5bを形成する際、段差底部1aに該当する層間絶縁膜3に深い接続孔5aを形成し、段差上部1bに該当する層間絶縁膜に浅い接続孔5bを形成することを同時に行う場合に、上記浅い接続孔5bの形成部位の底部にSiN等のエッチング速度の小さい材料層11bを予め形成しておく。

(もっと読む)

配線層形成方法及び配線構造

【目的】 落ち込み等の形状欠陥を有しない配線層を形成する方法を提供し、またそのような形状欠陥を有しない配線構造を提供する。

【構成】 本方法は、例えば基板の拡散領域と接続する配線層を絶縁膜上に形成する際に適用でき、絶縁膜12を貫通して形成されたコンタクトホール14をタングステン・プラグ34で埋め込み、かつ絶縁膜上にブランケット・タングステン膜20を形成するタングステン成膜工程と、基板面に直交する方向に所定深さまでブランケット・タングステン膜をエッチバックする第1エッチバック工程と、ブランケット・タングステン膜上に配線層22を形成する工程と、レジスト膜のマスクパターン24を形成する工程と、マスクパターンを使用して配線層をエッチングする配線層エッチング工程と、同じマスクパターンを使用してブランケット・タングステン膜をエッチバックする第2エッチバック工程とを備えている。

(もっと読む)

電界効果トランジスタの製造方法

【構成】 高速動作の可能なGaAsショットキー電界効果を用いたLDD構造の自己整合型FETにおいて、ゲート電極23a形成時のGaAs基板21へのダメージを少なくするために、該ゲート電極23aを薄膜とし、代わってSiO2 膜24を、サイドウォール26aの幅L11が充分な太さに形成され短チャネル効果を抑制することができるように、充分な厚さとする。前記サイドウォール26aは、SiO2 膜24よりもウエットエッチングによる速度が1/10以下と充分小さく、したがってエッチング後、引出配線28aを低抵抗に接合することができる。

【効果】 ゲート電極23aと引出配線28aとの接合にあたって、ゲート電極23aの表面に、ドライエッチングでは酸素などの不純物が導入されて高抵抗となってしまうのに対して、そのような不具合を防止することができる。

(もっと読む)

接続孔の形成方法

接続孔の形成方法

【目的】 アスペクト比が大きく開口径が微細であっても、上層配線膜の良好なカバレージや埋込み特性を保証できる接続孔を形成する。

【構成】 SiOx 層間絶縁膜2のエッチングを、異方性/等方性エッチングの組み合わせで行い、開口底よりも開口端の開口寸法が広いコンタクト・ホール2h1 を形成する。具体的には、(a)異方性形状を有するフォトレジスト・パターンをマスクとする異方性エッチングによりコンタクト・ホール2h1 を途中まで形成した後、マスク選択比を下げた等方性エッチングにより開口端の開口寸法を拡げるか、あるいは(b)逆テーパ状またはオーバーハング状のエッチング・マスクを介した等方性エッチングにより開口寸法の大きい開口端を形成した後、異方性エッチングにより開口底の開口寸法を規定しながらコンタクト・ホールを完成させる。

(もっと読む)

配線構造及びそのバイヤホール形成方法

【目的】 FET の配設密度を高める。

【構成】 GaAs基板10の基板面10a 上に順次に、n+-AlGaAs 導電層121 及びアンドープGaAs絶縁層122 設け、絶縁層122 上に複数のGaAsFET14 を設ける。各FET14を酸素イオン注入領域20により、電気的に絶縁分離する。そしてイオン注入領域20にFET14 のソース電極28の配設面から導電層121 に至る深さのバイヤホール32を設け、このバイヤホール32に設けた配線電極32を介して、ソース電極28と導電層121 とを接続する。また他方の基板面10b から導電層121 に至る深さのバイヤホール16を、基板10に設け、この基板面10b 全面にわたって設けた裏面電極36をバイヤホール16を介し導電層121 と接続する。バイヤホール32の深さを浅くできるのでバイヤホール径を小さくでき、従って絶縁層122 上に設けた複数のFET14 の集積密度を高めることができる。

(もっと読む)

配線構造及びそのバイヤホール形成方法

6,151 - 6,160 / 6,199

[ Back to top ]