国際特許分類[H01L21/283]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571) | 電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/283]の下位に属する分類

気体または蒸気からの析出,例.凝結 (1,528)

液体からの析出,例.電解液からの析出 (1,357)

国際特許分類[H01L21/283]に分類される特許

101 - 110 / 487

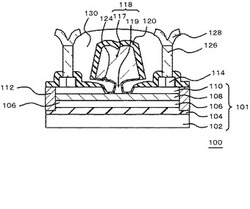

半導体装置およびその製造方法

【課題】ゲート電極の内部に腐食が進行することを抑制する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板101と、化合物半導体基板101上の一部に形成された接続部119と接続部119上に形成されかつ接続部119より幅広の本体部117とを有しており、かつアルミニウムを含むゲート電極118と、ゲート電極118の表面上に設けられた保護絶縁層(シリコン窒化膜120)と、シリコン窒化膜120が被覆していないゲート電極118の表面に設けられており、アルミニウムよりも酸化されにくい不動態膜124と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】長期にわたって信頼性に優れた半導体素子及びその製造方法を提供する。

【解決手段】基板の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板1の表面にレジスト組成物を塗布し、プリベークしてレジスト膜10を形成し、該レジスト膜10を貫通して第1表面電極1上にコンタクトホールを形成し、このコンタクトホール内にコンタクト電極4を形成し、第1表面電極2が形成された基板の表面に、熱膨張率が2ppm/℃以上7ppm/℃未満の第1絶縁膜3aを形成し、次いで、該第1絶縁膜3a上に熱膨張率が7ppm/℃以上24ppm/℃以下の第2絶縁膜3bを積層して絶縁膜3を形成し、コンタクト電極4を介して絶縁膜上に第2表面電極5を形成し、第1表面電極2、第2表面電極5及び絶縁膜3が形成された基板の裏面側を支持体に固定し、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

IGZO系アモルファス酸化物薄膜の製造方法及びそれを用いた電界効果型トランジスタの製造方法

【課題】導電体領域から絶縁体領域までの範囲内で所望の電気抵抗値有し、且つ、電気的ストレスに対して安定性の良好なIGZO系アモルファス酸化物薄膜を製造する

【解決手段】IGZO系アモルファス酸化物薄膜を基板上にスパッタ成膜し、その後アニール処理してIGZO系アモルファス酸化物薄膜を製造する方法であって、成膜装置内の水分量とアニール処理の温度の組み合わせを変化させて、導電体領域から絶縁体領域の範囲内の任意の電気抵抗値を有するアモルファス酸化物薄膜を製造する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】デバイス特性を維持し、ゲートリーク電流を低減できる電界効果トランジスタ及びその製造方法を提供する。

【解決手段】本発明に係る電界効果トランジスタ100は、III−V族窒化物半導体層構造と、半導体層構造上に離間して形成されたソース電極105及びドレイン電極106と、ソース電極105及びドレイン電極106の間に形成されたゲート電極108と、ソース電極105上及びドレイン電極106上に形成された電極保護膜107と、半導体層構造上に、ソース電極105、ドレイン電極106、ゲート電極108及び電極保護膜107の上面の少なくとも一部を覆うように形成され、半導体層構造を保護する第1のパッシベーション膜109を備え、第1のパッシベーション膜109は、所定の材料に対して化学的に活性であり、電極保護膜107は、所定の材料に対して化学的に不活性な金属である。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】絶縁性が高く、かつ均一な膜厚を有するゲート絶縁膜を効率よく形成することができる電界効果型トランジスタの製造方法、及び該電界効果型トランジスタの製造方法により製造され、安定した特性を有する高性能な電界効果型トランジスタの提供。

【解決手段】前記第一の基材上にゲート電極を形成するゲート電極形成工程と、第二の基材上にゲート絶縁膜形成用樹脂溶液を塗布し、ゲート絶縁膜を形成する塗布工程と、前記ゲート絶縁膜表面の流動性が消失するまで乾燥する乾燥工程と、前記ゲート電極と、前記ゲート絶縁膜表面とを接触させて接触体を形成する接触工程と、前記接触体に対し、ゲート絶縁膜形成用樹脂のガラス転移温度以上の熱を加える加熱工程と、前記接触体から前記第二の基材を剥離し、第一の基材上にゲート絶縁膜を形成する剥離工程とを少なくとも含む電界効果型トランジスタの製造方法である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧の異なるトランジスタが同一半導体基板上に混載されている場合においても、それらのトランジスタの性能が向上するようにストレスライナ膜を構成することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に混載された低耐圧トランジスタおよび高耐圧トランジスタ上に形成するストレスライナ膜11、12は、互いに膜質を異ならせることができる。ここで、ストレスライナ膜11は、低耐圧トランジスタの性能が効果的に改善され、高耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。また、ストレスライナ膜11は、高耐圧トランジスタの性能が効果的に改善され、低耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。

(もっと読む)

トランジスタ及びその製造方法

【課題】Siチヤネルを有するNMOSとSiGeチャネルを有するPMOSで、NMOSには引張り歪みを与える、PMOSには、表面のダングリングボンドを減少させることができる半導体装置を提供する。

【解決手段】単結晶シリコン基板50の一部領域にシリコンゲルマニウムチャネル膜54aを形成し、PMOSトランジスタを、シリコン膜60aを形成し、NMOSトランジスタを形成する。単結晶シリコン基板、シリコンゲルマニウムチャネル膜、PMOSトランジスタ、NMOSトランジスタの表面上に、反応ガス、雰囲気ガス及び水素ガスを含む蒸着ガスを用いて、シリコン窒化膜82を形成し、PMOSトランジスタは、シリコンゲルマニウムチャネル膜表面のダングリングボンドの除去により、ホールスキャタリングが抑制され、NMOSトランジスタには引張り歪みを与えることにより動作特性の改善ができる。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置

【課題】トランジスタ特性に優れ、ゲート絶縁膜のゲート電極の近傍の領域中で電荷や電界の集中が起こらない半導体装置を提供する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタのゲート絶縁膜は窒素原子及び酸素原子を含有する。ゲート絶縁膜は、半導体層に接する第1の面及びゲート電極に接する第2の面において窒素原子を含有せず、第1の面と第2の面の間に窒素原子濃度のピークを有する。

(もっと読む)

101 - 110 / 487

[ Back to top ]