国際特許分類[H01L21/283]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571) | 電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/283]の下位に属する分類

気体または蒸気からの析出,例.凝結 (1,528)

液体からの析出,例.電解液からの析出 (1,357)

国際特許分類[H01L21/283]に分類される特許

1 - 10 / 487

半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置およびその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置およびその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

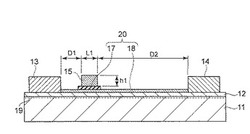

電界効果トランジスタ

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタを有する信頼性の高い半導体装置を提供する。

【解決手段】ガラス基板上に設けられたボトムゲート構造のスタガ型トランジスタを有する半導体装置において、ゲート電極層上に組成を異なる第1のゲート絶縁膜及び第2のゲート絶縁膜が順に積層されたゲート絶縁膜を設ける。又は、ボトムゲート構造のスタガ型トランジスタにおいて、ガラス基板とゲート電極層との間に保護絶縁膜を設ける。第1のゲート絶縁膜と第2のゲート絶縁膜との界面、又はゲート電極層とゲート絶縁膜との界面における、ガラス基板中に含まれる金属元素の濃度を、5×1018atoms/cm3以下(好ましくは1×1018atoms/cm3以下)とする。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】耐圧を向上できる電界効果トランジスタを提供する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

(もっと読む)

半導体装置とその製造方法

【課題】特性ばらつきの少ない絶縁ゲートを備えた窒化物半導体の半導体装置を提供すること。

【解決手段】 半導体装置が備える絶縁ゲートは、窒化物半導体層1上に設けられているアモルファスの酸化シリコン膜2と、酸化シリコン膜2上に設けられているゲート電極8を有している。ゲート電極8に対向する窒化物半導体層1が酸化されている。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】II族酸化物半導体を用いた半導体素子における新規な絶縁層形成技術を提供する。

【解決手段】半導体素子の製造方法は、(a)基板上方に、II族酸化物半導体層を成長させる工程と、(b)II族酸化物半導体層上に、窒素をドープしつつOリッチ条件での成長を行い抵抗率が105Ωcm以上のII族酸化物絶縁層を成長させる工程とを有する。

(もっと読む)

エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法

【課題】エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法を提供する。

【解決手段】基板上のゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上のグラフェンチャネルと、グラフェンチャネル上で互いに離隔しているソース電極及びドレイン電極と、ソース電極及びドレイン電極の上面を覆い、グラフェンチャネル上でソース電極とドレイン電極との間にエアギャップを形成するカバーと、を備えるグラフェントランジスタ。前記ソース電極と前記ドレイン電極との間の前記グラフェンチャネルの長さが、10nm〜100nmである。

(もっと読む)

1 - 10 / 487

[ Back to top ]