国際特許分類[H01L21/288]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571) | 電極用の導電または絶縁材料の析出 (3,372) | 液体からの析出,例.電解液からの析出 (1,357)

国際特許分類[H01L21/288]に分類される特許

51 - 60 / 1,357

半導体上の銅のめっき

【課題】前面電流トラックを形成したドープ半導体ウェハの銅めっきに関する改善された銅めっき方法を提供する。

【解決手段】前面、裏面およびPN接合を含む半導体を提供し、下層を含む導電トラックのパターンを前記前面が含み、かつ前記裏面が金属接点を含んでおり;前記半導体を一価銅めっき組成物と接触させ;並びに導電トラックの下層上に銅をめっきする。

(もっと読む)

金属パターン材料及びその製造方法

【課題】めっき後に細線乃至小ドットの金属パターンを高解像度で形成できる金属パターン材料及び金属パターン材料の製造方法の提供。

【解決手段】特定のめっき形成用光感応材料を6μm未満のピッチで露光する際に、6μmピッチ露光時の最適パワーに対し、100%未満であり、かつ〔(ピッチ(μm)×75/6+25)−30〕〜〔(ピッチ(μm)×75/6+25)+15〕%のレーザーパワーで露光する露光工程と、露光後のめっき形成用光感応材料を現像液で現像する現像工程と、現像後のパターンが形成されためっき形成用光感応材料を、めっき浴比が10未満でめっきを行うめっき工程とを含む金属パターン材料の製造方法である。

(もっと読む)

めっき装置及び半導体装置の製造方法

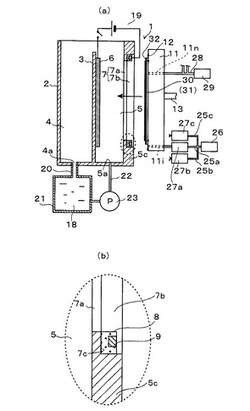

【課題】ウェハの周縁部で膜を正常に成長させることができるめっき装置を提供する。

【解決手段】めっき槽2内部に取り付けられた第1電極6と、めっき槽2の側壁5cにおいて、環状のフランジ7cを介してめっき槽2の内から外に向けて直径の小さい順に隣接する環状の第1、第2の開口部7a,7bと、第2の開口部7b内でフランジ7cの上に取り付けられるシールパッキン8と、シールパッキン8の上に、第2の開口部7bの内壁から離れて取り付けられる環状の第2の電極9と、第2の電極9に対向する位置に周縁を有するウェハ保持領域11xを有する第2の開口部7bよりも大きなウェハステージ11と、ウェハステージ11のウェハ保持領域11xの周囲の領域に形成され、シールパッキン8に一端が向けられる加圧用ホール11iと、ウェハステージ11を移動してめっき槽2の側壁5cに押し当てて前記第2の開口部7bを閉塞させる駆動部13とを有する。

(もっと読む)

無電解薄膜析出法により平坦化銅相互接続層を形成する方法および装置

【課題】基板に定形された形態部の内部に、表面が平坦化された導電性材料を形成する方法を提供する。

【解決手段】平坦化表面を形成する方法であって、狭小形態部と幅広形態部が形成された基板上に、第1のプロセスでは電気めっき法により狭小形態部および幅広形態部の少なくとも一部を充填し、第1の層を形成し、第2のプロセスでは無電解めっき法により幅広形態部のに対応する第1の層中の孔および第1の層上に第2の層を充填形成し、表面が平坦な上層部110を形成する。

(もっと読む)

半導体装置の製造装置および半導体装置の製造方法

【課題】2種類以上のめっきを同一の感光性材料を用いて選択的に成膜する場合、クラックの発生を抑制する。

【解決手段】この製造装置は、表面に絶縁膜330が形成された半導体ウェハ200表面

を第1のめっき液を用いてめっき処理する第1のめっき処理槽と、半導体ウェハ200表

面を第2のめっき液を用いてめっき処理する第2のめっき処理槽と、を備える。第1のめ

っき処理槽には、半導体ウェハ200の表面と重なる部分の長さがd1であり、かつ絶縁

膜330との接触幅がw1の第1のシール320が設けられ、第2のめっき処理槽には半

導体ウェハ200の表面と重なる部分の長さがd2であり、かつ絶縁膜330との接触幅

がw2の第2のシール340が設けられ、第1のシール320と第2のシール340の間

には、d2<d1−w1の関係が成り立っている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の一表面上に絶縁膜を介して形成された導電層と、半導体基板の他面上に形成されたバンプ部と、導電層とバンプ部とを接続する半導体基板を貫通する貫通電極部とを有する半導体装置を提供する。

【解決手段】半導体基板の他面側から導電層に接続する貫通孔を形成し、貫通孔及び他面上にメタル膜(バリアメタル及びシードメタル)6を形成し、その上にフォトレジスト10を形成し、貫通孔より大きなパターンに加工してメッキマスク層を形成し、電解メッキ法により銅からなる第1メッキ膜7を形成して、貫通電極部と第1バンプ部を形成し、第1バンプ部上に第2バンプ部となる第2メッキ膜8を形成する。

(もっと読む)

下地導電層付き基板の製造方法および貫通電極基板の製造方法

【課題】製造時間とコストの大幅な削減が可能な下地導電層付き基板および貫通電極基板の製造方法を提供する。

【解決手段】厚さ方向に複数の貫通孔2を有するガラス基板3の貫通孔2内に下地導電層4を有する基板の製造方法であって、前記ガラス基板3の貫通孔2内に、金属粒子と分散媒とを含有する流動性の導電性組成物(金属インク)の層を形成する工程と、この導電性組成物の層を加熱して、貫通孔2の内壁面に金属粒子の金属を主体とする下地導電層4を形成する工程とを備える方法である。貫通電極基板5の製造方法は、こうして形成された下地導電層4上に電解めっき等により導電性金属の層を形成して、貫通孔2内に充填された貫通電極6を形成する工程を有する。

(もっと読む)

素子及び太陽電池並びに電極用ペースト組成物

【課題】焼成時における銅の酸化が抑制され、良好なオーミックコンタクトを有する銅含有電極がシリコンを含む基板上に形成された素子及び該素子を構成するのに好適な電極用ペースト組成物を提供する。

【解決手段】シリコンを含む基板と、前記基板上に配置された電極とを有し、前記電極は、銅含有粒子、ガラス粒子、溶剤及び樹脂を含む電極用ペースト組成物の焼物であり、体積抵抗率が1×10−4Ω・cm以下である素子である。また電極用ペースト組成物に、リン含有銅合金粒子、錫含有粒子、ガラス粒子、溶剤及び樹脂を含ませ、25℃における粘度が80Pa・s〜1000Pa・sの範囲であるように構成する。さらにまた電極用ペースト組成物に、リン含有銅合金粒子、錫含有粒子、ガラス粒子、溶剤及び樹脂を含ませ、固形分濃度が70質量%〜98質量%の範囲であるように構成する

(もっと読む)

基板中間体、基板及び貫通ビア電極形成方法

【課題】貫通ビア電極を形成する際に処理温度が高くなく且つ低コストで、バリア層を均一に、且つ高い密着強度で製造する。

【解決手段】シリコン基板10の厚さ方向に形成された高アスペクト比の、貫通ビア電極形成用の孔12の内周面に、自己組織化単分子膜24を形成し、これに、金属ナノ粒子14を、高密度で吸着させて、この金属ナノ粒子14を触媒として、バリア層を無電解めっきにより形成し、バリア層の上にシード層を無電解めっきにより形成し、次に、貫通ビア電極材を電解めっきにより堆積して、孔12を埋めて、貫通ビア電極を形成する。

(もっと読む)

半導体装置の製造方法及びめっき装置

【課題】めっき膜の成膜が進んでも、被めっき面の表面電位と所望する表面電位との誤差が生じることを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

(もっと読む)

51 - 60 / 1,357

[ Back to top ]