国際特許分類[H01L21/288]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571) | 電極用の導電または絶縁材料の析出 (3,372) | 液体からの析出,例.電解液からの析出 (1,357)

国際特許分類[H01L21/288]に分類される特許

81 - 90 / 1,357

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタ及び薄膜トランジスタの製造方法を提供する。

【解決手段】薄膜トランジスタは、第1方向に形成された少なくとも1本のゲートラインを含むゲート11と、ゲート上に形成されたゲート絶縁層12と、ゲート絶縁層12上に形成された少なくとも1つのソース13及びドレイン14と、を含み、ソース13及びドレイン14のうち少なくともいずれか一つは、延長部分13b、14bを含み、延長部分13b、14bは、少なくとも1本のゲートラインと平行するように、第1方向に形成される。ゲート11は、ライン状に均一厚を有し、その側面と上面との間に曲面を含み、1本または2本以上のゲートラインを含む形態となる。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置および半導体装置

【課題】配線溝へのめっきの埋め込み性を安定させることができる半導体装置の製造方法等を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、めっき処理によって金属膜を埋め込んで検査パターン10を形成する形成工程と、検査パターン10の特性を検出する検出工程と、検出工程によって検出された検査パターン10の特性に基づいて、前記めっき処理の条件を調整する調整工程とを含む。前記形成工程は、3層以上の配線層11〜13に亘って形成され、かつ中間層にスタックドビア22を有するパターンを、前記検査パターン10として形成する。

(もっと読む)

銅めっき溶液およびこれを用いた銅めっき方法

【課題】高縦横比のビアホールを埋め込むのに好適な銅めっき溶液および銅めっき方法を提供する。

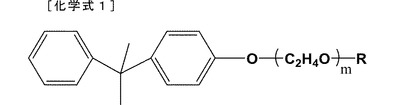

【解決手段】シード層を有する基板を浸漬し、水、銅供給源、電解物質、塩素イオン、第1添加剤、第2添加剤、および第3添加剤を含み、前記第1添加剤は、化学式1に示す化合物である銅めっき溶液を用いて銅めっきを行う。

(式中、Rは、水素原子または炭素原子数1〜6のアルキル基であり、mは、平均重合度であり6〜14の実数である。)

(もっと読む)

導電性パターン形成用組成物及び導電性パターンの形成方法

【解決手段】硬化性オルガノポリシロキサンと硬化剤とを含有するシリコーンゴム組成物に、最大粒径が1μm未満の導電性微粒子を配合してなることを特徴とする導電性パターン形成用組成物。

【効果】本発明の導電性パターン形成用組成物を用いることによって、インクジェット法やスタンプ法のような印刷方法により半導体基板上に微細な導電性パターンを塗布描画することができ、描画された回路を、組成物中に含まれる硬化剤によって架橋形成してゴム化することで、応力耐性を持つ導電性回路とすることができる。これにより、導電性回路の微細化が可能となると共に、信頼性の高い半導体回路を作製することができる。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜厚の制御を精度よく行う。

【解決手段】半導体基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含む半導体装置の製造方法において、めっき工程は、複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれる際に、所定の第1の基準電流密度を半導体基板全面における各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度でめっき処理を行う工程(S104)を含む。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

スプレー機構およびスプレー機構群

【課題】噴出される流体の原料の利用効率の向上を図る。

【解決手段】噴出口13から噴出領域に流体20を噴出するスプレーノズル10と、噴出口13が挿入される開口部31を有し、噴出口13からスプレーノズル10側とその反対側の噴出領域側とを仕切る仕切板30と、仕切板30の開口部31の近傍から噴出領域側に向けて、スプレーノズル10の軸方向に対して所定の角度で延設される側壁板40とを備える。側壁板40は、仕切板30および側壁板40を配置していない状態におけるスプレーノズルの集束前噴出領域の外側に配置される。スプレーノズル10から流体20を噴出させた際に、側壁板40と対向する側から集束前噴出領域に外気が流入することにより、噴出領域が側壁板40側に集束する。

(もっと読む)

段差構造体を有する基材上への銅導電膜の形成方法

【課題】画像表示装置の配線等として用いられる銅導電膜を形成する際に、生産性を大きく低下させることなく、段差構造体の最大線幅が最小線幅に対して4倍以上である場合においても均一なめっき高さでめっきを行ない、段差構造体間での抵抗ばらつきの小さい銅配線パターンを容易に形成できるようにする。

【解決手段】基材上に並列配置され、かつ最大線幅が最小線幅の4倍以上である複数の段差構造体を横断被覆する銅導電膜4の形成において、電解めっき液の液導電率を60S/m以上とし、かつ銅導電膜4の膜厚を段差構造体の最大高さに対して2倍以上とする。

(もっと読む)

ポリマー薄膜における自己整合ビアホールの形成

【課題】有機電界効果トランジスタにおけるビア形成を、低コストで効率的なプロセスで実現する。

【解決手段】誘電層106内にビア113を形成する際、まず各ビア位置にパターン化された導電材よりなるポストを印刷し、次にパターン化されていない誘電層106を堆積させ、次に第2のパターン化された導電層を堆積させる。ビア113は、誘電層106を堆積した後、第2の導電層を堆積する前に、ポストをフラッシュアニールすることにより形成される。

(もっと読む)

81 - 90 / 1,357

[ Back to top ]