国際特許分類[H01L21/316]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体上への絶縁層の形成,例.マスキング用またはフォトリソグラフィック技術の使用によるもの;これらの層の後処理;これらの層のための材料の選択 (16,787) | 無機物層, (4,431) | 酸化物またはガラス性酸化物または酸化物を基礎としたガラスからなるもの (3,052)

国際特許分類[H01L21/316]に分類される特許

1,001 - 1,010 / 3,052

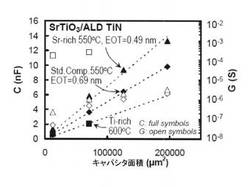

チタン酸ストロンチウムベースの誘電体層を有するキャパシタを備えたメモリセルの形成方法およびそれから得られるデバイス

【課題】低い等価酸化膜厚(EOT)および低い漏洩電流を有する金属−絶縁体−金属キャパシタを提供する。

【解決手段】低温原子層堆積(ALD)法を用いて、SrxTiyO3ベースの金属−絶縁体−金属(MIM)キャパシタを製造する方法が開示される。好ましくは、下部電極を形成するためにTiNが用いられる。キャパシタのSrxTiyO3誘電体層でのSr/Ti比率は、キャパシタの電気的特性を調整するために変化できる。SrxTiyO3誘電体層の誘電率および漏洩電流は、このSrxTi1−xO3誘電体層のSr含有量とともに単調に減少する。SrxTiyO3誘電体層とTiN下部電極との間の界面でのSr含有量を増加させることによって、界面の等価酸化膜厚(EOT)をさらに低減できる。

(もっと読む)

基板処理方法

【課題】膜厚が薄い場合や導入物質の濃度が低い場合であっても、導入物質を導入することのできる基板処理方法を提供する。

【解決手段】基板1上に薄膜2を形成する工程と、薄膜2に、導入物質のガスクラスターをイオン化して加速したガスクラスターイオンビーム3を照射して薄膜中2に導入物質を導入する工程とを具備し、基板1上に導入物質が導入された薄膜2を形成する。

(もっと読む)

成膜方法、成膜装置、圧電体膜、圧電素子、及び液体吐出装置

【課題】成膜する膜の組成及び基板サイズによらず、面内方向の組成等の膜特性を高度に均一化することが可能な成膜方法を提供する。

【解決手段】基板BとターゲットTとを対向させて、プラズマを用いた気相成長法により基板B上にターゲットTの構成元素を含む膜を成膜するに際して、ターゲットTの表面から基板B側に2〜3cm離れた位置のプラズマ空間のプラズマ電位Vs(V)の基板Bの面内方向のばらつきを±10V以内に調整して、成膜を行う。ターゲットTの表面から基板20側に2〜3cm離れた位置におけるガス圧力の基板Bの面内方向のばらつきを±1.5%以内に調整して、成膜を行うことが好ましい。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、良好な移動度を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 第一の発明の半導体装置は、基板と、基板表面に形成され、Geを主成分とする半導体領域と、半導体領域上に形成された非金属Ge化合物層と、非金属Ge化合物層上に形成された絶縁膜と、絶縁膜上に形成された電極と、前記電極を挟む前記基板表面に形成されたソース・ドレイン領域とを備えることを特徴とする。非金属Ge化合物層は、例えばSrとGeの化合物、BaとGeの化合物もしくはBaとSiとGeの化合物を有する。

(もっと読む)

半導体装置の製造方法

【課題】 耐湿性が低下し難いパシベーション膜を有する半導体装置の製造方法であって、より汎用性が高い製造方法を提供する。

【解決手段】 半導体装置の製造方法であって、基板上に第1パシベーション膜16を形成する工程と、第1パシベーション膜16にクラックを生じさせる工程と、クラックを生じさせた第1パシベーション膜16上に第2パシベーション膜18を形成する工程を備えていることを特徴とする半導体装置の製造方法。

(もっと読む)

シクロテトラシロキサンを重合に対し安定化する方法及び組成物

【課題】1,3,5,7−テトラメチルシクロテトラシロキサンのようなシクロテトラシロキサンを重合に対し安定化させるための方法、及び組成物を提供する。

【解決手段】有効量の遊離基スカベンジャー重合抑制剤をそのようなシクロテトラシロキサンに供給することを含む安定化方法、及び電子材料の製造においてケイ素酸化物の前駆物質として化学気相成長法で使用される重合に対し安定化させた、1,3,5,7−テトラメチルシクロテトラシロキサンのようなシクロテトラシロキサンの組成物であって、そのようなシクロテトラシロキサンと遊離基スカベンジャー重合抑制剤とを含むシクロテトラシロキサンの組成物である。

(もっと読む)

成膜方法および成膜装置

【課題】結晶化しており、かつリーク電流も小さいジルコニア系膜を成膜することができる成膜方法を提供すること。

【解決手段】真空保持可能な処理容器内に被処理体を挿入し、処理容器内を真空に保持した状態とし、処理容器内にジルコニウム原料と酸化剤とを交互的に複数回供給して基板上にZrO2膜を成膜する工程と、処理容器内にシリコン原料と酸化剤とを交互的に1回または複数回供給して基板上にSiO2膜を成膜する工程とを、膜中のSi濃度が1〜4atm%になるように供給回数を調整して行い、これら供給回数のZrO2膜成膜とSiO2膜成膜とを1サイクルとし、このサイクルを1以上行い所定膜厚のジルコニア系膜を成膜する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】SiO2/SiC構造を備える、たとえばMOSFETなどの半導体装置は、界面準位密度の低減が不十分である。

【解決手段】SiC基板1の一方の主表面上に形成させたSiCエピタキシャル層2の一方の主表面上に、あらかじめSi薄膜3を形成させて、このSi薄膜3の内部に窒素原子を注入させる。この状態で、SiCエピタキシャル層2の一方の主表面上を酸窒化させる。

(もっと読む)

Si含有膜の成膜方法、絶縁膜、並びに半導体デバイス

【解決手段】プラズマCVD法によるSi含有膜の成膜方法において、成膜原料として用いるシラン化合物として、反応性基として水素原子又はアルコキシ基を有すると共に、分子中には2個以上のケイ素原子を含有し、かつ2個以上のケイ素原子は飽和炭化水素基を介して結合され、かつ、アルコキシ基に含まれる炭素原子を除いた炭素原子数[C]とSi原子数[Si]の比[C]/[Si]が3以上であり、全てのケイ素原子は2以上の炭素原子と直接の結合を有するシラン化合物を用いるプラズマCVD法によるSi含有膜の成膜方法。

【効果】有効な成膜速度が得られると共に、膜の疎水性の確保と、ケイ素原子の求核反応に対する反応性の抑制を同時に達成することができ、膜の化学的安定性を確保することができる。

(もっと読む)

ペロブスカイト酸化物薄膜の製造方法及びペロブスカイト酸化物薄膜

【課題】 液相法によって所要機能を有するペロブスカイト酸化物薄膜を製造する方法、及びペロブスカイト酸化物薄膜を提供する。

【解決手段】 成膜対象のペロブスカイト酸化物を主成分とし、平均直径が略5nm以上略15nm以下の適宜直径のナノ結晶粒子を所定溶媒中に分散させた分散液を調製し(ステップS1)、この分散液中に、対象電極としての所定材料の基板と対向電極とを浸漬させ、両電極間に所定の電圧を印加することによって前記基板の表面に前記ナノ結晶粒子を、乾燥時の厚さが数十nm〜数百nmとなるように堆積させる(ステップS2)。そして、この基板を略400℃以上略800℃以下の適宜温度で焼成する(ステップS3)。

(もっと読む)

1,001 - 1,010 / 3,052

[ Back to top ]