国際特許分類[H01L21/3205]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体上への絶縁層の形成,例.マスキング用またはフォトリソグラフィック技術の使用によるもの;これらの層の後処理;これらの層のための材料の選択 (16,787) | 絶縁層へ非絶縁層,例.導電層または抵抗層,の付着;これらの層の後処理 (7,286)

国際特許分類[H01L21/3205]の下位に属する分類

後処理 (649)

国際特許分類[H01L21/3205]に分類される特許

1,001 - 1,010 / 6,637

基板貫通の相互接続部を形成する方法

【課題】表側と裏側とを有する基板を含むマイクロエレクトロニクス・デバイスに基板を貫通する相互接続部を形成する方法を提供する。

【解決手段】基板の表側に回路素子(134)を形成するステップと、回路素子(134)に達するトレンチ(138)を基板の裏側に形成するステップと、ポリマー絶縁材料からなる層(140)をトレンチ(138)内に形成するステップと、ポリマー絶縁材料からなる層(140)を基板の表側から露出させるために、回路素子(134)に開口(150)を形成するステップと、ポリマー絶縁材料からなる層(140)のうち開口(150)によって露出された部分を基板の表側から除去するステップと、回路素子(134)と電気的に通じている導電相互接続層(142)をトレンチ(138)内に形成するステップと、を有する。

(もっと読む)

半導体装置

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】半導体チップCP1には、スイッチ用のパワーMOSFETQ1,Q2と、パワーMOSFETQ1の発熱を検知するためのダイオードDD1と、パワーMOSFETQ2の発熱を検知するためのダイオードDD2と、複数のパッド電極PDとが形成されている。パワーMOSFETQ1およびダイオードDD1は、辺SD1側の第1MOSFET領域RG1に配置され、パワーMOSFETQ2およびダイオードDD2は、辺SD2側の第2MOSFET領域RG2に配置されている。ダイオードDD1は辺SD1に沿って配置され、ダイオードDD2は辺SD2に沿って配置され、ダイオードDD1,DD2間にソース用のパッド電極PDS1,PDS2以外の全てのパッド電極PDを辺SD3に沿って配置している。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】より容易に半導体装置を製造すること。

【解決手段】薄型化した基板15の下面に支持フィルム19を貼付し、その支持フィルム19をフレーム40に貼付することで、損傷しやすい基板15をフレーム40ごと取り扱うことを可能にして、基板15の搬送や基板15に対する加工を行ない易くした。また、その基板15に再配線27、柱状電極20、半田端子23や、基板15の上面及び側面を被覆する封止膜9を形成した後、ダイシングにより個片化した際、基板15に貼付した支持フィルム19をそのまま下面を被覆する樹脂膜とすることで、半導体装置1をより容易に製造することとした。

(もっと読む)

半導体装置およびその製造方法

【課題】高容量・高精度なMIM静電容量素子を少ない工程で製造する技術を提供する。

【解決手段】第1層間絶縁膜17上に静電容量素子の下部電極21と第2層配線22とを同時に形成した後、第1層間絶縁膜17上に堆積した第2層間絶縁膜24に開口部34を形成する。次に、開口部34内を含む第2層間絶縁膜24上に順次堆積した容量絶縁膜27、第2金属膜および保護金属膜29を順次堆積し、第2層間絶縁膜24上の保護金属膜29、第2金属膜および容量絶縁膜27をCMP法で研磨・除去することによって、開口部34内に容量絶縁膜27、第2金属膜からなる上部電極28および保護金属膜29を残す。

(もっと読む)

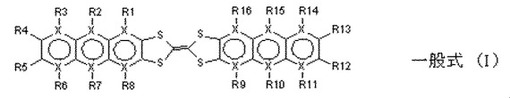

有機積層膜

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の配線における電気的干渉を低減する。

【解決手段】半導体装置1Aにおける接続パッド12と半田端子23を繋ぐ電流経路となる配線を、半導体基板11を覆う下地絶縁膜14上に形成された下層配線17と、下地絶縁膜14を覆うフィルム材19上に形成された上層配線21とを組み合わせて構成するとともに、半導体基板11から比較的離間した位置に配されて、下層配線17よりも半導体基板11と電気的に干渉しにくくなっている上層配線21の割合を高くするように、上層配線21を下層配線17よりも長く形成することとした。

(もっと読む)

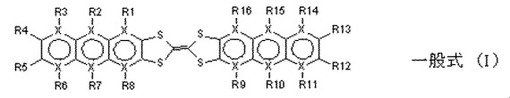

新規有機導電性膜を使用した有機電極

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ディッシングを抑制することができる半導体装置の構造を実現する。

【解決手段】半導体装置200は、基板(シリコン基板)と、基板上に設けられた絶縁層(層間絶縁膜201)と、層間絶縁膜201に設けられた第1の配線溝と(配線溝202)、配線溝202に埋め込まれた第1の金属膜(Cuめっき膜206)と、を備え、配線溝202の底部が、凸部形状を有する。

(もっと読む)

金属薄膜の形成方法

【課題】スパッタリングによる成膜レートを低くし、被処理体の表面に形成されたアスペクト比が3以上の孔または溝の内壁面および内底面に被覆性が良好な金属薄膜を形成し、少ない電力でも、ターゲットにおける自己保持放電を発生させる成膜方法を提供する。

【解決手段】ターゲット3に電圧Vおよび電流Iを印加しチャンバ2内でターゲットから放電が発生した後、スパッタガスの導入を止めてターゲットのイオンにより自己保持放電を発生させ、被処理体Wの表面の孔または溝内を含む被処理体の表面全面に金属薄膜を形成する工程において、ターゲットに印加する電流Iを一定とし、放電が不安定になった時に電圧Vを増大させるとともに、関係式(1)および(2)を満たすことを特徴とする。I>I0・・・(1)、P>P0・・・(2)(I0:自己保持放電を開始する電流の最小値、P:ターゲットの電力、P0:自己保持放電を開始する電力の最小値)

(もっと読む)

1,001 - 1,010 / 6,637

[ Back to top ]