国際特許分類[H01L21/322]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体の内部性質の改変,例.内部不完全性の形成 (657)

国際特許分類[H01L21/322]に分類される特許

81 - 90 / 657

シリコンウェーハの製造方法

【課題】無欠陥領域[P]が全域に分布する無欠陥のシリコンウェーハであっても、IG効果が有効に得られるシリコンウェーハの製造方法を提供する。

【解決手段】シリコン単結晶インゴットから切り出した無欠陥のシリコンウェーハに、NH3を含むガス雰囲気中でRTA処理を施して、ウェーハ内部に新たに空孔を形成させ、その後に、窒素、酸素またはこれらの混合ガス雰囲気中で、700℃から900℃までを3℃/分以下の速度で昇温し、900〜1100℃で1〜8時間保持する熱処理を施して、ウェーハ内部にBMDを形成させる。さらに、エピタキシャル処理を施して、ウェーハ表面にエピタキシャル層を成長させる。これにより、IG効果を有するとともに一層表面品質に優れた無欠陥のシリコンウェーハを得ることができる。

(もっと読む)

シリコンウェーハの製造方法

【課題】COP等のgrown−in欠陥が表層域に存在しない、例えば直径450mmの大口径のシリコンウェーハを製造する方法を提供する。

【解決手段】チョクラルスキー法により3.0℃/分以下の冷却速度の下に育成したシリコン単結晶をスライスしてシリコンウェーハを製造するに当たり、該シリコンウェーハに非酸化性雰囲気中で熱処理を施し、次いで酸化性雰囲気で熱処理を施し、シリコンウェーハの表面側にgrown−in欠陥が存在する欠陥層および該欠陥層の直下にgrown−in欠陥が存在しない無欠陥層を形成し、その後前記欠陥層を研磨除去する。

(もっと読む)

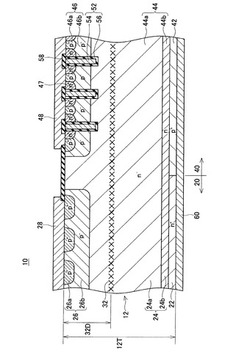

半導体装置

【課題】 ダイオード領域とIGBT領域が混在した半導体装置において、トレンチゲートのそれぞれの閾値電圧のばらつきを抑制するとともに、逆回復特性を改善することを目的とする。

【解決手段】 半導体装置10の半導体層12には、ダイオード領域20とIGBT領域40の双方に亘って連続して伸びているとともに、半導体層12の表面から観測して第1深さと第2深さの間の範囲に設けられている第1ライフタイム制御領域32が形成されている。第1深さは、トレンチゲート52の底面の深さと一致している。第2深さは、半導体層12の厚みを1.0としたときに0.4である。

(もっと読む)

シリコンウェーハの熱処理方法

【課題】ウェーハ製造後のデバイス作製工程においてスリップが発生することのないシリコンウェーハを提供するための熱処理方法を提供する。

【解決手段】デバイス作製工程において、シリコンウェーハが受ける熱応力に起因してシリコンウェーハにスリップが発生する限界である臨界せん断応力と、シリコンウェーハの製造段階で施す熱処理を経た該ウェーハにおける酸素析出物のサイズLに対する残存酸素濃度Coの比Co/Lとの相関を、デバイス作製工程の温度条件毎に予め求めること、シリコンウェーハを供する実際のデバイス作製工程の温度条件に対応する相関に基づいて、実際のデバイス作製工程においてシリコンウェーハが受けるせん断応力を超える臨界せん断応力に対応するCo/Lを求めること、該Co/L以上となる条件の下に熱処理を施すことを特徴とする。

(もっと読む)

シリコンウェーハの熱処理方法

【課題】シリコンウェーハに対してRTPを行う際、シリコンウェーハの裏面の外周部をリング状に保持するサセプタを用いても、接触痕やスリップの発生を効果的に抑制することができるシリコンウェーハの熱処理方法の提供。

【解決手段】ウェーハWの回転数を250rpm以上350rpm以下とし、ウェーハWの半導体デバイスが形成される表面W1側及び前記表面W1側に対向する裏面W2側に不活性ガスを供給し、かつ、最高到達温度を1300℃以上1400℃以下として、急速加熱・急速冷却熱処理を行う。

(もっと読む)

シリコンウェーハ及びその製造方法

【課題】板状酸素析出物を含むシリコンウェーハであってデバイスプロセスにてLSA処理を行った場合であっても転位の発生を防止することが可能なシリコンウェーハを提供する。

【解決手段】本発明によるシリコンウェーハは、LSA処理を含むデバイスプロセスに供せられるシリコンウェーハであって、LSA処理時においてシリコンウェーハに含まれる板状酸素析出物の対角線長をS(nm)、前記LSA処理における最高到達温度をT(℃)とした場合、T×S2≦9×106を満たす。本発明によれば、上記の条件でLSA処理を行うことにより、シリコンウェーハに含まれる板状酸素析出物を起点とした転位の発生を防止することが可能となる。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、及びSOI基板の作製方法

【課題】半導体基板の再生に適した方法、半導体基板の再生に適した方法を用いた再生半導体基板の作製方法、及び当該再生半導体基板を用いたSOI基板の作製方法の提供を目的とする。

【解決手段】損傷した半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層が除去されるエッチング処理と、半導体基板を構成する半導体材料を酸化する物質、酸化された半導体材料を溶解する物質、及び、半導体材料の酸化の速度及び酸化された半導体材料の溶解の速度を制御する物質、を含む混合液を用いて、未損傷の半導体領域に対して損傷半導体領域が優先的に除去されるエッチング処理と、レーザ光照射工程と、を行うことで半導体基板を再生する。

(もっと読む)

半導体基板の作製方法及び半導体装置の作製方法

【課題】平坦性の高い表面を有する単結晶半導体層を備えた半導体基板の作製方法を提供することを目的の一とする。平坦性の高い単結晶半導体層を備えた半導体基板を用いて信頼性の高い半導体装置を作製することを目的の一とする。

【解決手段】半導体基板の作製工程において、単結晶半導体基板に希ガスイオン照射工程、レーザー照射工程および水素イオン照射工程を行うことで、単結晶半導体基板の所定の深さに大きな結晶欠陥を含有した薄い脆化領域を形成し、剥離加熱工程を行うことで脆化領域より表面側の単結晶半導体層をベース基板に転載する。

(もっと読む)

エピタキシャルウェーハの製造方法、エピタキシャルウェーハ及び撮像用デバイスの製造方法

【課題】欠陥のほとんどないシリコンエピタキシャル層を形成できるエピタキシャルウェーハの製造方法、当該方法により製造されたエピタキシャルウェーハ及び撮像用デバイスの製造方法を提供することを目的とする

【解決手段】前記シリコン基板に急速熱処理を施すことによって、少なくとも前記シリコン基板の表面から0.5μmの深さまでの領域に存在するRIE法により検出される欠陥を消滅させるRIE欠陥消滅工程と、前記RIE法により検出される欠陥を消滅させたシリコン基板の表面上に前記シリコンエピタキシャル層を形成する工程とを具備するエピタキシャルウェーハの製造方法。

(もっと読む)

半導体装置の製造方法

【課題】半導体ウェハから得られる複数のメインチップにおいて、メインチップ毎のON電圧のバラツキを低減することが可能な半導体装置の製造方法を提供する。

【解決手段】IGBT素子1と、小面積のトランジスタ2とが表面に形成された半導体ウェハ10を準備する。半導体ウェハ10の表面全体に電子線等を照射する。IGBT素子1およびトランジスタ2の中に再結合中心を形成する。測定装置15によりトランジスタ2のON電圧を測定しつつ、IGBT素子1およびトランジスタ2において規定されたライフタイムを所定のアニール処理を施すことにより回復させる。ライフタイムが回復しているとき、制御装置16は、IGBT素子1のON電圧がそれぞれ所定のON電圧となるように、測定されたトランジスタ2のON電圧に基づいてアニール処理におけるアニール処理量を制御する。

(もっと読む)

81 - 90 / 657

[ Back to top ]