国際特許分類[H01L21/76]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 構成部品間の分離領域の形成 (3,154)

国際特許分類[H01L21/76]の下位に属する分類

国際特許分類[H01L21/76]に分類される特許

31 - 40 / 2,201

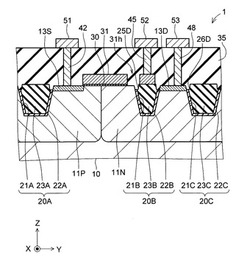

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

半導体装置

【課題】オフリーク電流の抑制および駆動電流の増大を図ることが可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置において、ゲート電極は、第1および第2のソース・ドレイン領域の間に設けられた第1リセス内に少なくとも一部がゲート絶縁膜を介して埋め込まれて第1および第2のソース・ドレイン領域よりも深い位置まで形成される。チャネルは、素子領域においてゲート絶縁膜に隣接して第1および第2のソース・ドレイン領域の間に形成される。一対の応力付与部は、素子分離領域において、ゲート電極のゲート幅方向に垂直な面内において第1および第2のソース・ドレイン領域の下部のチャネルと重複する領域に設けられ、素子分離領域の構成材料と異なる絶縁材料からなりチャネルに対してゲート幅方向の両側から応力を付与する。

(もっと読む)

トレンチ内に誘電層を形成する方法

【課題】半導体構造の形成方法、より具体的にはトレンチ内における誘電層の形成方法を提供する。

【解決手段】半導体構造を形成する方法は、基板上にシリコン酸化被膜を形成するために、シリコン前駆体と原子酸素前駆体を約150℃以下の処理温度において反応させることを含む。シリコン酸化被膜は酸素含有環境内で紫外線(UV)硬化される。

(もっと読む)

半導体装置およびその製造方法

【課題】論理素子のnチャネルMOSトランジスタに十分な膜厚の引張応力膜を形成し、メモリ素子がゲート電極間の層間絶縁膜の埋込不良を生じない製造方法の提供。

【解決手段】論理素子は、第1及び第2のnチャネルMOSトランジスタを含み、第1のゲート高さGH1及び第1のゲート長を有するゲート電極を有し、ゲート電極は第1の間隔Dを有し、メモリ素子は、第3および第4のnチャネルMOSトランジスタを含み、ゲート高さGH2および第2のゲート長を有するゲート電極を含み、論理素子及びメモリ素子は第1の引張応力膜64で覆われ、論理素子は、さらに第2の引張応力膜65で覆われ、論理素子及びメモリ素子のゲート間に形成された引張応力膜の最小距離は各々第1の距離LL及び第1の距離LMで隔てられ、第1のアスペクト比(GH1/LL)と、第2のアスペクト比(GH2/LM)とは略等しい。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体チップの側面に逆バイアス印加時の漏れ電流を防ぐための分離層を有する該半導体チップを備えた半導体装置において、十分な逆耐圧性能を与えるための不純物の導入を短時間で行なうことができ、デバイスピッチやチップサイズの縮小が図れ、量産プロセスにも適した半導体装置及びその製造方法を提供する。

【解決手段】ウェハのダイシングラインに沿ってレーザーを照射して、そのウェハの表面又は所定深さのウェハ内にクラック起点を形成し、そのクラック起点を伸展させることで半導体チップの個片化を行って、亀裂などのダメージの少ない清浄なダイシング面を形成し、そのダイシング面に不純物を導入して、逆耐圧性能を与えるため分離層を形成する。

(もっと読む)

半導体メモリ

【課題】素子間リークを低減できる半導体メモリを提供する。

【解決手段】本実施形態の半導体装置は、第1のゲート絶縁膜上の電荷蓄積層と、第1の絶縁体を介して電荷蓄積層上に設けられる制御ゲート電極とを含むメモリセルと、アクティブ領域AAH上の第2のゲート絶縁膜20Hと、第2のゲート絶縁膜上の第1の電極層21Hと、を含むトランジスタHTと、素子分離絶縁膜15H上に設けられるシールドゲート電極SIGと、を有する。シールドゲート電極SIGの底部は、素子分離絶縁膜15Hの最も高い上面より半導体基板10の底部側に位置している。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

半導体基板の製造方法および半導体装置の製造方法

【課題】エッジ部に形成される段差部の傾斜を緩やかにできるSON構造を有する半導体基板の製造方法およびその半導体基板を用いた半導体装置の製造方法を提供する。

【解決手段】第1ホール群13の外周部に第1ホール11より直径D2が小さく間隔W2が大きな第2ホール群14を形成し、その後の水素雰囲気の高温アニールで平板状の空洞を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

半導体メモリ及びその製造方法

【課題】素子分離絶縁膜の応力に起因する素子特性の劣化を低減する。

【解決手段】本実施形態の半導体メモリは、第1のゲート絶縁膜上の電荷蓄積層と電荷蓄積層上に積層される制御ゲート電極とを含む第1のアクティブ領域AA内のメモリセルMCと、第2のゲート絶縁膜20L上の第1の電極層21Lと、を含む、第2のアクティブ領域AAL内の第1のトランジスタLTとを具備する。第2のアクティブ領域AALを定義する第2の素子分離絶縁膜19Xは、第1の膜190と、第1の膜190と第2のアクティブ領域AALとの間の第2の膜195とを含み、第1の膜190の上面は、第2の膜195の上面よりも、半導体基板10の底部側に位置している。

(もっと読む)

31 - 40 / 2,201

[ Back to top ]