国際特許分類[H01L21/76]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 構成部品間の分離領域の形成 (3,154)

国際特許分類[H01L21/76]の下位に属する分類

国際特許分類[H01L21/76]に分類される特許

61 - 70 / 2,201

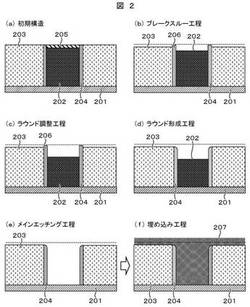

ドライエッチング方法

【課題】本発明は、ダミー材料の除去により形成される溝や孔に容易にトップラウンドを設けることができるドライエッチング方法を提供する。

【解決手段】本発明は、層間酸化膜に周囲を囲まれたダミー材料を除去することにより溝または孔を形成するドライエッチング方法において、前記ダミー材料を所定の深さまでエッチングし、前記エッチング後に等方性エッチングを行い、等方性エッチング後に前記ダミー材料の残りを除去することを特徴とするドライエッチング方法である。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】ランプアニールによるレイアウトに起因した温度バラつきを低減する。

【解決手段】この半導体装置10は、基板100と、基板100に埋め込まれた素子分離領域200と、基板100のうち、素子分離領域200の無い領域に形成された不純物層(エクステンション領域322、ソース領域324、エクステンション領域342、及びドレイン領域344)と、を備える。この素子分離領域200は、たとえば、波長300nm以上890nm以下においてSiO2よりも光吸収係数が大きい材料から形成されている光吸収層220を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜の膜厚が異なる複数のトランジスタを有する半導体装置において、オフリークの増加を抑制する。

【解決手段】半導体装置は、半導体層上に形成された第1MISトランジスタ及び第2MISトランジスタを備える。第1MISトランジスタは、活性領域101が素子分離膜102に囲まれた第1活性領域と、第1活性領域上に第1ゲート絶縁膜111を介して形成された第1ゲート電極104とを有する。第2MISトランジスタは、活性領域101が素子分離膜102に囲まれた第2活性領域と、第2活性領域上に第2ゲート絶縁膜103を介して形成された第2ゲート電極104とを有する。第2ゲート絶縁膜103は、第1ゲート絶縁膜111よりも薄い。第2MISトランジスタは、少なくとも第2ゲート電極104の下方において、第2活性領域と素子分離膜102との境界部上に、素子分離膜102の側面を覆う保護絶縁膜108を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】フォトダイオードを有する半導体イメージセンサーにおいて、より高い光検出効率を実現し、光検出部以外の信号処理を行う画素トランジスタの特性を安定させることで、半導体装置の微細化を可能にする。

【解決手段】フォトダイオードPDを構成するP+領域126およびN型領域111に炭素を共注入して炭素注入層128a、128bを形成することで、フォトダイオードPDの容量を増大させる。また、炭素注入層128bの形成によりN型領域111を含む転送トランジスタTrのチャネル内のホウ素の分布を均一化し、転送トランジスタTrの特性を安定させることで半導体装置内の素子の特性ばらつきの発生を防ぐ。

(もっと読む)

固体撮像装置及びその製造方法、電子機器

【課題】画素分離部の幅を縮小することや光電変換部の面積の拡大することを可能にする固体撮像装置を提供する。

【解決手段】第1導電型の電荷蓄積領域23を含む光電変換部及び画素トランジスタTr1から成る画素38と、画素38が複数配列された画素領域と、この画素領域内の隣接する画素38間の半導体層22に設けられたトレンチ42の内壁部に形成された、エピタキシャル成長による第1導電型の半導体層43と、この第1導電型の半導体層43の内部に形成され、隣接する画素38の電荷蓄積領域23を分離する、画素分離部41とを含んで、固体撮像装置21を構成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させ、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板に、複数の第1の素子領域と、素子分離領域と、第2の素子領域を形成する。第1の素子領域上に、メモリセルゲート電極、2本の選択ゲート電極を形成し、第2の素子領域に周辺ゲート電極を形成する。第1の絶縁膜を形成し、周辺ゲート電極の側壁部上が開口される第1のレジストパターンを形成し、第1のエッチング処理を行い、側壁絶縁膜を形成する。第2のレジストパターンを形成し、第2のエッチング処理を行い、選択ゲート電極側壁部の第1の絶縁膜を除去する。第2の絶縁膜を堆積し、第3の絶縁膜を堆積する。2本の選択ゲート電極間上が開口される第3のレジストパターンを形成し、第3のエッチングおよび第4のエッチング処理を行い、コンタクトホールを形成する。

(もっと読む)

半導体装置の製造方法、半導体装置、SOI基板の製造方法およびSOI基板

【課題】SOI基板のチャージ蓄積による不良を抑制する。

【解決手段】まず、シード基板100の一面に、シード基板100の表面と同一面を形成するように、開口部220を有する絶縁層200を形成する(絶縁層形成工程)。次いで、シード基板100の一面に接するように、支持基板300を貼り合せる(貼り合せ工程)。次いで、シード基板100または支持基板300の一方を薄板化することにより、当該薄板化基板からなる半導体層120を形成する(半導体層形成工程)。以上の工程により、SOI基板を準備する。次いで、半導体層120に半導体素子60を形成する(半導体素子形成工程)。

(もっと読む)

トレンチ埋め込み用樹脂組成物

【課題】基体に形成されたトレンチ内に酸化シリコンを埋め込むために使用するのに好適なトレンチ埋め込み用樹脂組成物を提供すること。

【解決手段】本発明に係るトレンチ埋め込み用樹脂組成物は、酸化シリコン粒子をトレンチ埋め込み用樹脂組成物全体に対して0.35重量%以上2.20重量%以下で、並びに、一般式(1)〜(3)で表される化合物の合計に対して、一般式(1):Si(OR1)4で表されるテトラアルキシキシラン化合物を45mol%以上87mol%以下で、一般式(2):R2Si(OR1)3で表されるトリアルコキシシラン化合物を10mol%以上50mol%以下で、そして一般式(3):R22Si(OR1)2で表されるジアルコキシシラン化合物を1.5mol%以上3.6mol%以下で含有する。

(もっと読む)

逆阻止絶縁ゲート型バイポーラトランジスタとその製造方法

【課題】ダイシング工程や搬送中の振動などの衝撃があって割れやクラックが生じても、IGBTの逆方向耐圧が劣化しないような逆阻止絶縁ゲート型バイポーラトランジスタおよびその製造方法を提供すること。

【解決手段】n型半導体基板の表面側にMOSゲート構造を有する活性領域と該活性領域の周囲の耐圧構造部とを有し、裏面側にはp型コレクタ層を備え、前記耐圧構造部の外周部に、前記表面側と前記裏面側とを繋ぐように配置されるp型分離層が裏面側で前記p型コレクタ層に電気的に接続される構成を有する逆阻止絶縁ゲート型バイポーラトランジスタにおいて、前記p型分離層が裏面側の前記p型コレクタ層に接続する部分における、基板面に平行方向の幅が60μm以上である逆阻止絶縁ゲート型バイポーラトランジスタとする。

(もっと読む)

61 - 70 / 2,201

[ Back to top ]