国際特許分類[H01L21/761]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 構成部品間の分離領域の形成 (3,154) | PN接合 (106)

国際特許分類[H01L21/761]に分類される特許

1 - 10 / 106

半導体装置

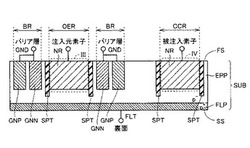

【課題】注入元素子から被注入素子への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】第1および第2の主表面を有する半導体基板SUB内にはエピタキシャル層EPPと、n型不純物領域NRを含む注入元素子と、注入元素子と間隔を隔てて形成された被注入素子と、注入元素子と被注入素子との間の領域の少なくとも一部に形成され、注入元素子と被注入素子とを結ぶ方向に対して交差する方向に延在する接地電位が印加されたn型領域GNNおよびp型領域GPPを有するバリア層BRとを備える。さらに半導体基板SUB内でエピタキシャル層EPPに接するように形成されたフローティングp型裏面領域FLPを有する。

(もっと読む)

半導体装置

【課題】バルク半導体基板上に形成されるトンネルトランジスタ同士を電気的に分離することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板内に形成された第1および第2の素子分離絶縁膜とを備える。さらに、前記装置は、前記第1および第2の素子分離絶縁膜間の前記半導体基板上に、ゲート絶縁膜を介して形成されたゲート電極を備える。さらに、前記装置は、前記半導体基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記半導体基板内に前記第1および第2の素子分離絶縁膜に接するように形成され、前記第1および第2の主端子領域の下面よりも深い位置に上面を有する、前記第2導電型の第1の拡散層を備える。

(もっと読む)

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

逆阻止絶縁ゲート型バイポーラトランジスタとその製造方法

【課題】ダイシング工程や搬送中の振動などの衝撃があって割れやクラックが生じても、IGBTの逆方向耐圧が劣化しないような逆阻止絶縁ゲート型バイポーラトランジスタおよびその製造方法を提供すること。

【解決手段】n型半導体基板の表面側にMOSゲート構造を有する活性領域と該活性領域の周囲の耐圧構造部とを有し、裏面側にはp型コレクタ層を備え、前記耐圧構造部の外周部に、前記表面側と前記裏面側とを繋ぐように配置されるp型分離層が裏面側で前記p型コレクタ層に電気的に接続される構成を有する逆阻止絶縁ゲート型バイポーラトランジスタにおいて、前記p型分離層が裏面側の前記p型コレクタ層に接続する部分における、基板面に平行方向の幅が60μm以上である逆阻止絶縁ゲート型バイポーラトランジスタとする。

(もっと読む)

固体撮像装置および固体撮像装置の製造方法

【課題】本発明の一つの実施形態の目的は、素子分離特性を向上可能な固体撮像装置および固体撮像装置の製造方法を提供することである。

【解決手段】実施形態によれば、固体撮像装置の製造方法が提供される。固体撮像装置の製造方法は、素子分離領域形成工程と、電荷蓄積領域形成工程とを含む。素子分離領域形成工程では、第1導電型の半導体層をエピタキシャル成長させて光電変換素子間を分離する素子分離領域を形成する。電荷蓄積領域形成工程では、第2導電型の半導体層をエピタキシャル成長させて前記光電変換素子における電荷蓄積領域を形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】STIの形成によるウェル拡散層の不純物濃度の変化を抑制し、かつ、ウェル拡散層のドーズロスを抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。メモリセル領域には、複数のメモリセルが半導体基板上に形成されている。周辺回路領域には、複数のメモリ素子を制御する複数の半導体素子が形成されている。素子分離領域は、複数のメモリセル間を分離し、あるいは、複数の半導体素子間を分離する。周辺回路領域において半導体素子が形成されているアクティブエリアの不純物濃度は、半導体基板の表面に対して水平方向に素子分離領域の側面からアクティブエリアの内部へ向かって低下している。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

半導体装置の製造方法

【目的】SON構造上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置あわせをすることができる半導体装置の製造方法を提供すること。

【解決手段】シリコンウェハ1のダイシングライン4などの無効領域の内部にSON構造11のアライメントマーク9を形成し、このアライメントマーク9を赤色レーザ(透過型レーザ)の反射光16の変化で認識することで、図示しないSON構造23上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置合わせをすることができる。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】小さいサイズでラッチアップの発生を防止できる半導体装置を提供する。

【解決手段】第1導電型の半導体基板1と、前記半導体基板内に形成された第1導電型の第1ウェル領域4と、前記半導体基板内に形成され、第1ウェル領域と隣り合う領域に配置された第2導電型のエピタキシャル領域2と、前記エピタキシャル領域内下方の領域に形成され、前記エピタキシャル領域よりも不純物濃度が高い第2導電型の埋め込み領域6と、第1ウェル領域と前記エピタキシャル領域及び前記埋め込み領域との境界に形成されたトレンチ8と、第1ウェル領域上に形成され、第2導電型のソース及びドレイン領域を有する第1半導体素子と、前記エピタキシャル領域上に形成され、第1導電型のソース及びドレイン領域を有する第2半導体素子と、を備える。

(もっと読む)

1 - 10 / 106

[ Back to top ]