国際特許分類[H01L21/768]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 装置内の別個の構成部品間に電流を流すため使用する相互接続を適用するもの (5,422)

国際特許分類[H01L21/768]に分類される特許

1,001 - 1,010 / 5,422

半導体装置

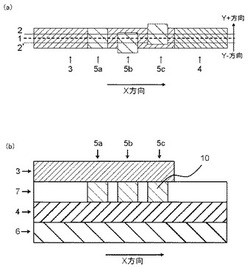

【課題】配線上に配列されて形成されている複数のビアの少なくとも一部が冗長ビアでも、目ズレによる複数の冗長ビアの全滅を防止できる半導体装置を提供する。

【解決手段】半導体装置は、線形の配線4上に配列されて形成されている複数のビア5(5a-5c)を有し、複数のビア5の少なくとも一部が冗長ビア5として形成されており、ビア5の少なくとも一部が配線4の中心線から変位した位置に形成されている。従って、フォトレジストパターニング時に配線4とビア5に目ズレが発生した場合でも、少なくとも冗長ビア5の一つは目ズレの影響が少なく形成できる。

(もっと読む)

配線構造体、半導体素子、配線基板、表示用パネル及び表示装置

【課題】 酸化物電極との良好な接続を行うことや、絶縁膜等との界面で生じる相互拡散を抑制することができ、かつ製造工程の低コスト化を図ることができる配線構造体、それを用いた半導体素子、配線基板、表示用パネル及び表示装置を提供する。

【解決手段】 アルミニウム層、銅層及び銅合金層からなる群より選択される少なくとも1つの層と、アルミニウム合金層とを含む2層以上の積層体であり、該アルミニウム合金層が表層に配置されている配線構造体である。これにより、液晶表示装置等において、酸化物電極と配線との接続部で酸化膜が形成されず、良好な接続を行うことができる。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】第1のソース電極、ゲート電極、ドレイン電極、及び第2のソース電極が、所定方向に沿ってこの順に並んで半導体基板の上面上に形成された構造を有するトランジスタを形成する。犠牲層を、トランジスタを覆って半導体基板の上面上に形成する。犠牲層を部分的に除去することにより、第1のソース電極及び前記第2のソース電極を露出する。第1のソース電極及び第2のソース電極に接続され、所定方向に沿って延在する配線を、犠牲層の上面上に形成する。犠牲層を除去する。上面が開口した枠体を、トランジスタの周囲を取り囲んで、半導体基板の上面上に形成する。枠体上にテープを貼り付けることにより、枠体及びテープによってトランジスタ及び配線を覆う。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の接続孔側壁の寸法制御を高精度に且つ低コストで行うことができる半導体装置を提供する。

【解決手段】半導体装置1は、基材10の主面を被覆し、下部電極11の上面に達する接続孔12hを有する絶縁膜12を備える。絶縁膜12の膜密度は、基材10の主面から絶縁膜12の厚み方向に離れるに従って低減する。接続孔12hの内径は、絶縁膜12の膜密度の低減に伴って拡大する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】複数のゲート電極3bを覆うように窒化シリコン膜(第1絶縁膜)5を形成した後、オゾンTEOS膜(第1酸化シリコン膜)6、プラズマTEOS膜(第2酸化シリコン膜)を順次積層する。ここで、オゾンTEOS膜6を積層後、プラズマTEOS膜を積層する前に、窒化シリコン膜5をCMPストッパ膜として、CMP法により研磨する。これにより、プラズマTEOS膜の膜厚を均一化させることができるので、半導体装置の信頼性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ストレッサ膜を有する半導体装置及びその製造方法に関し、ストレッサ膜からの応力を効率よくチャネル領域に印加してMISFETの電流駆動能力を向上しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に、素子領域を画定する素子分離絶縁膜を形成し、素子領域上に、ゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板内にソース/ドレイン領域を形成し、ゲート電極及びソース/ドレイン領域が形成された半導体基板上に第1の絶縁膜を形成し、素子分離絶縁膜の端部に生じた窪み内に第1の絶縁膜が残存するように第1の絶縁膜をエッチバックし、半導体基板上に、半導体基板の表面に平行な方向に応力を印加する第2の絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38上に第1ストッパ膜39及び第2ストッパ膜40を形成する工程と、第1領域2を覆う第1マスク60をマスクとし、第1ストッパ膜をストッパとして、第2領域4内の第2ストッパ膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の第2ストッパ膜をサイドエッチングする工程と、第2ストッパ膜とエッチング特性が異なる第2応力膜42を形成する工程と、第2領域を覆い、第1領域側の端面が第2ストッパ膜上に位置する第2マスクとし、第2ストッパ膜をストッパとして、第2応力膜の一部が第1応力膜の一部及び第2ストッパ膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

半導体装置とその作製方法

【課題】特性が良好なトランジスタを提供する。

【解決手段】例えば、ボトムゲート・ボトムコンタクト構造のトランジスタを作製するに際して、ソースとドレインを構成する導電層を3層の積層構造とし、2段階のエッチングを行う。すなわち、第1のエッチング工程には、少なくとも第2の膜及び第3の膜に対するエッチングレートが高いエッチング方法を採用し、第1のエッチング工程は少なくとも第1の膜を露出するまで行う。第2のエッチング工程には、第1の膜に対するエッチングレートが第1のエッチング工程よりも高く、「第1の膜の下に接して設けられている層」に対するエッチングレートが第1のエッチング工程よりも低いエッチング方法を採用する。第2のエッチング工程後にレジストマスクをレジスト剥離液により剥離するに際し、第2の膜の側壁が少し削られる。

(もっと読む)

1,001 - 1,010 / 5,422

[ Back to top ]