国際特許分類[H01L21/768]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 装置内の別個の構成部品間に電流を流すため使用する相互接続を適用するもの (5,422)

国際特許分類[H01L21/768]に分類される特許

1,041 - 1,050 / 5,422

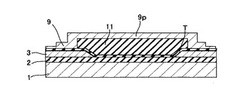

半導体装置及びその製造方法

【課題】Cdsubの低減を通じて、出力容量Cossの低減に寄与する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板と半導体基板上に絶縁膜を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域内に、第2導電型の半導体層からなるウェルを形成するとともに、ウェル内および第1導電型の活性領域内に、第1導電型の半導体層からなるソース・ドレイン領域を形成した横型MOSFETにおいて、活性領域のうち、ドレイン領域にコンタクトするように形成されるドレインパッド形成領域9p下の少なくとも一部は、SOI基板の絶縁膜に到達するように形成された絶縁性領域11で構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ダイシング等で半導体装置を個片化する際に加工のダメージ又は膜の残留応力などに起因して発生する、基板上の膜の剥離を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置101,102の周辺すなわち個片化のための加工ラインの近傍の基板1上に溝6を形成する。その溝の内部では基板上に成膜される薄膜が少なくとも1部で不連続となることにより、万一、半導体装置の端部から膜剥がれが発生したとしても、この溝部でその進行を阻止する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体集積回路の高集積化と機能素子の高性能化とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板1の表面領域に配置されるスイッチ素子3,4と、下面がスイッチ素子3,4に接続されるコンタクトプラグ6と、コンタクトプラグ6の上面の直上に配置される機能素子7とを備える。コンタクトプラグ6の上面の最大表面粗さは、0.2nm以下である。

(もっと読む)

半導体装置の製造方法

【課題】信頼性が損なわれるのを防止しつつ、電気的特性の良好な半導体装置を提供する。

【解決手段】半導体基板10上に、化学気相堆積法により、シリコンと酸素と炭素とを含む絶縁膜42を形成する工程と、絶縁膜を形成する工程の後、350℃以下の温度で加熱しながら絶縁膜に対して紫外線キュアを行う工程と、紫外線キュアを行う工程の後、絶縁膜に対してヘリウムプラズマ処理を行う工程とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置においてショートを生じることを防ぐことができる、半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板に所定の間隔で設けられた一対の不純物拡散領域と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側面及び前記ゲート絶縁膜の両側面を覆う、絶縁性の一対のサイドウォールスペーサーと、ゲート電極の上面に形成されたシリサイド金属膜と、を備える。サイドウォールスペーサーは、上下に積み重ねられた下部サイドウォールスペーサーと上部サイドウォールスペーサーとを有する。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】生産性を向上した一括加工型3次元積層メモリ構成の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、積層構造体MLと、選択ゲート電極SGと、半導体ピラーSPと、記憶層48と、内側絶縁膜42と、外側絶縁膜43と、選択ゲート絶縁膜SGIと、を備えた不揮発性半導体記憶装置が提供される。積層構造体は、第1方向に積層された複数の電極膜61と、電極間絶縁膜62と、を有する。選択ゲート電極は、積層構造体と積層された複数の選択ゲート導電膜71と、選択ゲート導電膜間絶縁膜72と、を有する。半導体ピラーは、積層構造体及び選択ゲート電極を第1方向に貫通する。記憶層は、電極膜と半導体ピラーとの間に、内側絶縁膜は、記憶層と半導体ピラーとの間に、外側絶縁膜は、記憶層と電極膜との間に、選択ゲート絶縁膜は、選択ゲート導電膜と半導体ピラーとの間に設けられる。

(もっと読む)

回路基板及びその製造方法

【課題】配線抵抗が低く配線間の絶縁性の高い回路基板及びその製造方法を提供する。

【解決手段】基板上に、Cuを含む導電性材料の配線構造体を形成し、配線構造体の表面に、Cu−N結合を有する絶縁性の拡散防止膜を形成した後、拡散防止膜が形成された配線構造体を覆うように、絶縁膜を形成する。

(もっと読む)

1,041 - 1,050 / 5,422

[ Back to top ]