国際特許分類[H01L21/768]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 装置内の別個の構成部品間に電流を流すため使用する相互接続を適用するもの (5,422)

国際特許分類[H01L21/768]に分類される特許

1,081 - 1,090 / 5,422

半導体装置および半導体装置の製造方法

【課題】ビア深さのバラツキを抑制することができる半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に、SiおよびCを含むキャップ絶縁膜を形成する工程と、キャップ絶縁膜上に、キャップ絶縁膜と比較して、シリコン原子数に対する炭素原子数の組成比が高い、有機シリカ膜を形成する工程と、不活性ガス、Nを含むガス、フッ化炭素ガスおよび酸化剤ガスを含む混合ガスを用いたプラズマ処理により、有機シリカ膜に、異なる開口径を有する2以上の凹部を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】どのようなレイアウトの配線に対しても、個々の配線ごとにエアギャップ部を設ける。エアギャップ部によって、配線の寄生容量を低減する。

【解決手段】半導体装置は、層間絶縁膜と、層間絶縁膜内に埋め込まれた配線と、配線の側面と層間絶縁膜との間に設けられたエアギャップ部と、を有する。半導体装置の製造方法は、配線の側面上に第2のサイドウォール膜を形成した後、第2のサイドウォール膜の一部が露出するように第1の絶縁膜を形成する。次に、第2のサイドウォール膜を除去することによりサイドスペースを形成した後、サイドスペースが埋め込まれないように第2の絶縁膜を形成することによりサイドスペースから構成されるエアギャップ部を形成する。

(もっと読む)

空隙組込みの構造体及び方法

【課題】 空隙を組み込んだ構造体及びその形成方法を提供する。

【解決手段】 VLSI及びULSI用の空隙含有金属・絶縁体相互接続構造体を、光パターン化可能低k材料を用いて作成する方法、及び形成した空隙含有金属・絶縁体相互接続構造体を開示する。より具体的には、本明細書で説明する方法は、内部に種々異なる深さの空隙がフォトリソグラフィにより画定された光パターン化可能低k材料の内部に構築される相互接続構造体を提供する。本発明の方法においては、空隙を形成するのにエッチ・ステップは必要としない。光パターン化可能低k材料内部の空隙を形成するのに、エッチ・ステップを必要としないで、本発明において開示する方法は、高信頼性の相互接続構造体を提供する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタのソースまたはドレインに電気的に接続され、上面がスイッチングトランジスタの上面よりも高い位置にあるコンタクトプラグと、コンタクトプラグの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】配線層の平坦性を維持しつつ、配線とインダクタとの間に生じる寄生容量を低減させた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に形成された第1の層間絶縁膜506と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた配線106と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた第1のダミーパターン107と、第1の層間絶縁膜506のうちインダクタ領域内に位置する部分に埋め込まれた第2のダミーパターン108と、第1の層間絶縁膜506の上方に形成された第2の層間絶縁膜と、第2のダミーパターン108の上方であって、第2の層間絶縁膜のうちインダクタ領域内に位置する部分に埋め込まれたインダクタ111とを備える。第2のダミーパターン108として金属が形成されていない。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

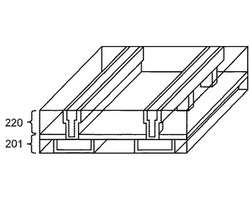

他の素子の処理の間のメモリセルの活性層の保護

【課題】メモリ構造に対して損傷を与えることを防止しながら選択された導電体から表面酸化物を適切に除去する。

【解決手段】導電層(102)を設け、その導電層(102)を覆うように誘電体(100)を設け、その誘電体(100)を貫通する第1および第2の開口(104,106)を設け、第1および第2の開口(104,106)内にそれぞれ第1および第2の導電体(108,110)を設けかつ第1および第2の導電体(108,110)を導電層(102)に接触させ、その第1の導電体(108)を覆うようにメモリ構造(126)を設け、そのメモリ構造(126)を覆うように保護要素(134)を設け、その第2の導電体(110)上に処理を施すことによる電子構造の製造方法。

(もっと読む)

薄膜素子用基板の製造方法、薄膜素子の製造方法、薄膜トランジスタの製造方法、薄膜素子、および薄膜トランジスタ

【課題】本発明は、表面平滑性に優れ、薄膜素子の特性劣化を抑制することが可能な薄膜素子用基板が得られる新規な薄膜素子用基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、金属基材に薬液処理を施す金属基材表面処理工程と、上記金属基材上にポリイミド樹脂組成物を塗布して絶縁層を形成する絶縁層形成工程とを有し、上記絶縁層の表面粗さRaが30nm以下であることを特徴とする薄膜素子用基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

1,081 - 1,090 / 5,422

[ Back to top ]