国際特許分類[H01L21/768]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 装置内の別個の構成部品間に電流を流すため使用する相互接続を適用するもの (5,422)

国際特許分類[H01L21/768]に分類される特許

41 - 50 / 5,422

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

貫通電極基板の製造方法

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板の製造方法は、ウェハ状の基板に前記基板を貫通しない複数の有底孔を形成し、前記基板及び前記有底孔の表面に絶縁膜を形成し、前記有底孔が開口する側の前記基板及び前記有底孔の絶縁膜上に金属からなるシード膜を形成し、前記シード膜に第1の時間直流電流を供給する電解めっき法により、前記シード層が形成されている面の前記有底孔の底部に金属層を形成し、前記シード膜及び前記金属層にパルス電流を供給する電解めっき法により、前記有底孔内に金属材料を充填して導通部を形成し、前記有底孔が形成されている側と反対側の前記基板の表面を、前記導通部の表面が露出するまで研磨する。

(もっと読む)

コンタクトホールの形成方法および電気光学装置の製造方法

【課題】シュリンク技術を利用して、コンタクトホールとして利用できる複数の凹部を1回のレジストマスク工程で異なる深さ寸法に形成することのできるコンタクトホールの形成方法、および電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置の素子基板10上にコンタクトホールを形成するにあたって、まず、第1開口部17aおよび第2開口部17bを備えたレジストマスク17を層間絶縁膜42の表面に形成した後、第1開口部17aおよび第2開口部17bから層間絶縁膜42および絶縁膜49をエッチングする。その後、シュリンク工程において、レジストマスク17を変形させて第2開口部17bを塞ぐ一方、第1開口部17aの開口面積を狭める。次に、第1開口部17aから層間絶縁膜41およびゲート絶縁層2をエッチングする。

(もっと読む)

半導体製造装置及び半導体製造方法

【課題】エッチング工程を行う際の窒化膜のエッチング選択比を向上できる半導体製造装置及び方法が提供される。

【解決手段】本発明による半導体製造装置は工程チャンバーの外部で供給されるジフルオロメタンCH2F2、窒素N2、及び酸素O2ガスからプラズマを発生させ、発生されたプラズマを工程チャンバー内へ供給する。プラズマが工程チャンバーへ供給される途中に三フッ化窒素NF3が供給される。このような装置構造及びソースガスを利用してシリコン窒化膜をエッチングすると、他の種類の膜に対するシリコン窒化膜のエッチング選択比を大きく増加させることができる。

(もっと読む)

絶縁膜形成方法及び絶縁膜形成装置

【課題】信号遅延の抑制と絶縁性の向上との両立が可能な絶縁膜形成方法及び絶縁膜形成装置を提供する。

【解決手段】

シリコン貫通電極用の貫通孔が形成されたシリコン基板を備える基板Sに絶縁膜を形成するに際し、抵抗加熱ヒータ33Hによって加熱された基板Sを収容する反応室31Sに、酸素ガス及びキャリアガスであるアルゴンガスと混合されたZr(BH4)4を供給する。そして、Zr(BH4)4を上記基板S上で熱酸化することによって、基板Sの表面及び上記貫通孔の内側面にジルコニウム、ホウ素、及び酸素を含む絶縁膜の一つであるZrBO膜を形成する。

(もっと読む)

半導体集積回路装置

【課題】チップあたりの端子数の増大に伴って、フリップチップ実装が種々の形態で実施されている。しかし、バンプピッチの微細化およびバンプの鉛フリー化によって、エレクトロマイグレーション耐性の確保がますます重要となっている。

【解決手段】本願の発明は、フリップチップ型の半導体集積回路装置において、チップの第1の主面上に形成された多数のUBMパッド状の各々に設けられた半田バンプの中間部には、上下を分割する前記半田バンプとは異なる材質の金属隔壁が設けられているものである。

(もっと読む)

基板の処理方法及びテンプレート

【課題】基板の所定位置に高い位置精度で処理液を供給し、当該基板を適切に処理する。

【解決手段】ウェハWのアライメント領域13上に純水Pを供給する(図9(a))。テンプレート20をウェハWの上方に配置する(図9(b))。純水PによってウェハWの処理領域12の上方にテンプレート20のめっき液流通路30が位置するように、テンプレート20とウェハWを位置調整する(図9(c))。テンプレート20を下方に移動させる(図9(d))。めっき液流通路30にめっき液Mを供給する(図9(e))。テンプレート20の第1の親水領域41と処理領域12との間にめっき液Mを充填する(図9(f))。めっき処理を行い、ウェハWの貫通電極10上にバンプ110を形成する(図9(g))。

(もっと読む)

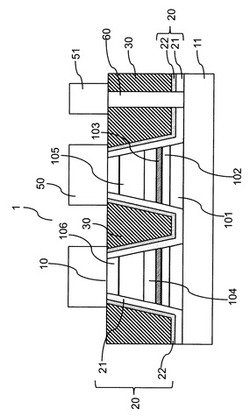

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

エッチング装置及び方法

【課題】基材の幅全体をエッチングして、埋め込まれた表面構造を露出させる方法を提供すること。

【解決手段】基材の表面をその幅の全体にわたりエッチングして材料を実質的に均一に除去すること、当該エッチング処理の間エッチングされる面に光を当てること、当該面から反射又は散乱した光に端部検出技術を適用して、埋め込まれた表面構造の出現を検出すること、そして当該埋め込まれた表面構造の検出に応じエッチングを修正することを含むエッチング方法。基材をその幅の全体にわたりエッチングして、埋め込まれたを露出させるためのエッチング装置も開示される。

(もっと読む)

半導体装置およびその製造方法、電子部品

【課題】貫通電極の微細化と表面電極の縮小化とを両立することができる半導体装置、および表面電極の大きさに関わらず、表面電極に対して貫通電極を確実にコンタクトさせることができる半導体装置の製造方法を提供すること。

【解決手段】Si基板29の表面13に複数の絶縁膜リング32を選択的に形成し、絶縁膜リング32の開口42に対向するように表面パッド33を形成する。次に、Si基板29を裏面14からエッチングすることにより、絶縁膜リング32の開口42を通過して表面パッド33に達する貫通孔56を形成し、貫通孔56の側面にビア絶縁膜35を形成した後、貫通孔56に電極材料を充填することにより、表面パッド33に電気的に接続されるように貫通電極17を形成する。

(もっと読む)

41 - 50 / 5,422

[ Back to top ]