国際特許分類[H01L21/82]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684)

国際特許分類[H01L21/82]の下位に属する分類

基板がシリコン技術を用いる半導体であるもの (27,844)

基板がIII−V技術を用いる半導体であるもの

基板がII−VI技術を用いる半導体であるもの

基板がグループ21/822,21/8252または21/8254の1つに包含されない技術を用いる半導体であるもの

基板が21/822,21/8252,21/8254または21/8256に包含される技術の組み合わせを用いる半導体であるもの

基板が半導体本外以外のもの,例.絶縁体本外のもの (4)

国際特許分類[H01L21/82]に分類される特許

41 - 50 / 3,836

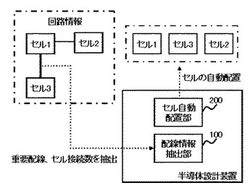

半導体設計装置、半導体設計方法及びプログラム

【課題】信号の重要度を考慮に入れたセルの自動配置を行うアルゴリズムは存在しない。従って、重要配線が不必要に長くなる場合がある。重要配線が長くなると、重要配線を伝達する信号を劣化させる原因となり得る。そのため、信号の重要度を考慮に入れたセルの自動配置を行うことで、重要度の高い信号の品質を維持する半導体装置を設計できる半導体設計装置、が望まれる。

【解決手段】半導体設計装置は、半導体装置に含まれる複数のセルを接続する複数の信号配線から、伝達する信号が重要であることを示す重要配線情報が付された重要配線と、複数の信号配線のそれぞれに接続されているセルの数を示すセル接続数と、を抽出する配線情報抽出部と、配線情報抽出部が抽出した重要配線及びセル接続数に応じて、複数のセルの配置を決定するセル自動配置部と、を備えている。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】半導体集積回路の回路面積を小さくする。

【解決手段】被試験回路2の観測対象の複数の信号線TA1〜TA4上の観測点TP1〜TP4を複数の入力端子に接続し、複数の信号線TA1〜TA4を伝搬する値の、論理積、論理和、否定論理積、または否定論理和の何れかを演算し、複数の信号線TA1〜TA4の何れかを伝搬する値に応じた出力値を出力する論理回路(NOR回路3,NAND回路4)を設けることで、複数の観測点をEOR回路を用いて共用する半導体集積回路より回路面積を小さくできる。

(もっと読む)

半導体装置

【課題】ヒューズ開口部からの水分侵入による電特異常及び配線腐食を防止する半導体装置を提供する。

【解決手段】ヒューズ配線4の下方には凸領域となるTEOS膜14の下敷きがあり、ヒューズ配線4はTEOS膜14を跨ぐように設けられ、ヒューズ配線4の上方にはTEOS膜14よりも小さい領域のヒューズ開口部13が設けられる。さらに、TEOS膜14の無い領域にてヒューズ配線14の両端に設けられたヒューズ端子15には第1金属配線7が電気的に接続されている。

(もっと読む)

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

半導体装置

【課題】ヒューズ開口部からの水分侵入による電特異常及び配線腐食を防止する半導体装置を提供する。

【解決手段】シリコン基板1上に絶縁膜2とゲート酸化膜3を設け、ゲート酸化膜2上の一部にヒューズ配線4の両端にヒューズ端子15を有するヒューズを設ける。ヒューズを構成するヒューズ配線4の上方には酸化膜5を介して窒化膜14が形成された凸領域があり、ヒューズ端子15は第1金属配線7と電気的に接続している。

(もっと読む)

半導体装置、パラメータ最適化方法、及びプログラム

【課題】トランジスタの容量の各成分や配線容量を分離してパラメータを最適化することが可能な半導体装置、パラメータ最適化方法、及びプログラムを提供すること。

【解決手段】MOSトランジスタから構成されたプリミティブゲート回路11aを奇数段でリング状に結合した第1リングオシレータ部11の各前記プリミティブゲート回路の出力部と電気的に接続された負荷部12となる第1配線を有する配線負荷パターンと、第2リングオシレータ部の各プリミティブゲート回路の出力部が第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、第3リングオシレータ部の各プリミティブゲート回路の出力部が第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、を備え、複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、複数の拡散層負荷パターンは、パターンごとに容量負荷が異なる。

(もっと読む)

局所優先方向アーキテクチャ、ツール、及び機器

【課題】「局所優先方向」配線モデルを使用してネットをルーティングするための機器を提供する。

【解決手段】本発明の一部の実施形態は、1つ又はそれよりも多くのEDAツール(プレーシング、ルーティングなどのような)と共に使用される「局所優先方向(LPD)」配線モデルを提供する。LPD配線モデルは、少なくとも1つの配線層が、各々が特定の配線層とは異なる優先方向を有する一組の領域を有することを可能にするものである。更に、各領域は、その組における少なくとも1つの他の領域の局所優先方向とは異なる局所優先方向を有する。更に、少なくとも2つの領域は、2つの異なる多角形形状を有し、その組における領域は、その組における別の領域を取り囲むことはない。

(もっと読む)

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

抵抗変化素子及びそのプログラミング方法

【課題】誤書き込み、及び誤動作を防止し、高信頼化、及び高密度化が可能な抵抗変化素子の提供。

【解決手段】第一の電極(201)と、抵抗変化膜(202)と、第二の電極(203)と、中間絶縁膜(204)と、制御電極(205)と、をこの順に積層した積層構造を備え、前記抵抗変化層(202)と前記中間絶縁膜(204)が直接接していない。

(もっと読む)

配線支援方法及び装置

【課題】配線すべき複数の信号線を、ユーザの指定する目的に従って適切にグループ化する。

【解決手段】配線すべき複数の信号線を複数のグループに分けるための方法は、ユーザから、複数の信号線のグループ化の条件の指定を受け付けるステップと、指定された、グループ化の条件と、データ格納部に格納されている、複数の信号線の始点端子群と終点端子群との配置パターンとに基づいて、複数の信号線のグループ化の処理を切り替えて実施する実施ステップとを含む。

(もっと読む)

41 - 50 / 3,836

[ Back to top ]