国際特許分類[H01L21/82]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684)

国際特許分類[H01L21/82]の下位に属する分類

基板がシリコン技術を用いる半導体であるもの (27,844)

基板がIII−V技術を用いる半導体であるもの

基板がII−VI技術を用いる半導体であるもの

基板がグループ21/822,21/8252または21/8254の1つに包含されない技術を用いる半導体であるもの

基板が21/822,21/8252,21/8254または21/8256に包含される技術の組み合わせを用いる半導体であるもの

基板が半導体本外以外のもの,例.絶縁体本外のもの (4)

国際特許分類[H01L21/82]に分類される特許

1 - 10 / 3,836

閾値テーブルの作成方法、クロストーク解析の悲観性削減方法、クロストーク解析方法、及びクロストーク解析プログラム

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体集積回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

ビア故障から保護するための方法及び構造

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

スタンダードセル、および、半導体集積回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

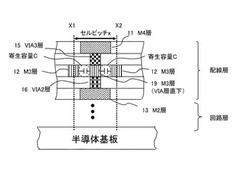

半導体装置の配線構造セルおよび半導体装置のレイアウト設計タイミング調整方法

【課題】複数の動作条件においてもタイミング制約を満たすように遅延時間を調整することを可能にする。

【解決手段】本発明に係る半導体装置の配線構造セルHSCは、M3層に、プロセス基準値bを満たす矩形に形成されたM3層19と、M3層19からプロセス基準値aを満たすよう離間し、口字型に形成されたM3層12と、M3層19の上にプロセス基準値を満たす矩形に形成されたVIA3層15と、M4層にVIA3層15に接して、プロセス基準値cを満たす幅で伸長した矩形に形成されたM4層11と、M3層19の下にVIA3層15と同じ平面形状に形成されたVIA2層16と、M2層にVIA2層16に接して、M4層11と同じ平面形状に形成されたM2層13と、を有するものである。

(もっと読む)

半導体集積回路

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

(もっと読む)

ダミーパターンの設計方法

【課題】金属配線パターンの寄生抵抗を低減可能なダミーパターンの設計方法を提供する。

【解決手段】切り欠きパターン2を一及び逆方向に各所定値Δx1だけ縮小して縮小図形4を生成した後、各所定値Δx1だけ拡大してダミーパターン5を生成し、その外形を抽出して矩形図形6を生成した後、各所定値Δx1だけ縮小して縮小図形7を生成し、ダミーパターン5から縮小図形7を論理減算して切り欠き図形8及び矩形図形9を生成し、切り欠き図形8を抽出してダミーパターン5から論理減算して矩形図形10を生成した後、各所定値Δx1だけ縮小して縮小図形11を生成し、矩形図形10から縮小図形11を論理減算して第1,第2のビア配置領域12,13を生成し、各ビア配置領域12,13にビア14をそれぞれ配置する。

(もっと読む)

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

1 - 10 / 3,836

[ Back to top ]