国際特許分類[H01L21/8222]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | バイポーラ技術 (534)

国際特許分類[H01L21/8222]の下位に属する分類

縦型トランジスタと横型トランジスタの組み合わせからなるもの (23)

併合トランジスタ論理または集積注入論理からなるもの (1)

相補型装置,例.相補型トランジスタ (50)

メモリ構造 (10)

国際特許分類[H01L21/8222]に分類される特許

1 - 10 / 450

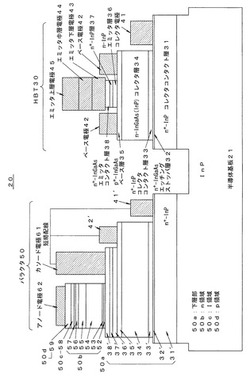

バラクタダイオードおよび半導体集積回路

【課題】狭い範囲の電圧変化に対して容量が線形的に、大きく変化する特性を実現する。

【解決手段】InPの半導体基板21上にエピタキシャル結晶成長させた層に対するエッチング処理により形成されるバラクタダイオード50において、半導体基板21上にエピタキシャル結晶成長させた層には、p型不純物を高濃度にドープさせバンドギャップエネルギーが半導体基板21よりも小さい材料からなるp領域50dと、p領域50dの半導体基板21寄りの面に接し、不純物をドープさせない材料または不純物を低濃度にドープさせた材料からなるI領域50cと、I領域50cの半導体基板21寄りの面に接し、n型不純物を中濃度以上にドープさせバンドギャップエネルギーが半導体基板21よりも大きい材料からなり、I領域50cから半導体基板21側に向かう程不純物濃度が低下する濃度減少部(54〜57)を有するn領域50bが含まれている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】バーティカル型のバイポーラトランジスタにおいて、エミッタ領域からベース領域にかけて存在する界面準位を安定に低減することを可能とした半導体装置とその製造方法を提供する。

【解決手段】バーティカル型のバイポーラトランジスタ10は、シリコン基板1に形成されたP型のベース領域13と、シリコン基板1に形成されてベース領域13に接するエミッタ領域15と、シリコン基板1の表面であってベース領域13とエミッタ領域15との境界部21上に形成されたシリコン酸化膜17と、シリコン酸化膜17上に形成されたポリシリコンパターン19と、を有する。シリコン酸化膜17とシリコン基板1との界面に塩素が1×1017cm−3以上の濃度で存在する。

(もっと読む)

半導体デバイス

【課題】高い電流増幅率と高いアーリー電圧を両立することができ、CMOSトランジスタとともに製造する場合でもより少ない製造工程により製造することができる半導体デバイスを提供する。

【解決手段】基板P11の表面に形成された第1導電型のベースP14と、ベースの表面に形成された第2導電型のエミッタN23と、ベースの表面においてエミッタと離間して配置され、エミッタから第1の種類のキャリアを受け取るとともに、その第1の種類のキャリアをベースへ注入する、第2導電型のドープ領域N24と、ベースを挟んで、エミッタおよびドープ領域の反対側に形成された、第2導電型のコレクタN15とを備える。

(もっと読む)

半導体装置

【課題】ホールド電圧が高いエミッタ・ベース短絡型の保護素子が設けられた半導体装置を提供する。

【解決手段】半導体装置1は、基板10と、前記基板上に形成された第1導電形の半導体層11と、前記基板と前記半導体層との間に形成された第1導電形の埋込層13と、前記半導体層上に形成された第2導電形のウェル14と、前記半導体層上であって、前記ウェルから離隔し、前記埋込層の直上域に形成された第1導電形の第1コンタクト層15と、前記ウェル上に形成された第2導電形の第2コンタクト層16と、前記ウェル上であって、前記第1コンタクト層と前記第2コンタクト層との間に形成された第1導電形の第3コンタクト層17と、前記埋込層と前記第1コンタクト層との間に形成され、前記第1コンタクト層に接した第1導電形のディープ層18と、を備える。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】成長時間を短縮してスループットを向上することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に、電子供給層6,10及びチャネル層8を有する高電子移動度トランジスタ構造層3を形成する工程と、高電子移動度トランジスタ構造層3上に、コレクタ層14、ベース層15、エミッタ層16及びノンアロイ層18を有するヘテロバイポーラトランジスタ構造層4を形成する工程と、を有するトランジスタ用エピタキシャルウェハの製造方法において、ヘテロバイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下で、かつ、一定の成長温度で成長するようにした。

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタポリシリコンに対する良好なコンタクトを得ることができる半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】ラテラル・バイポーラトランジスタを有する半導体装置であって、ラテラル・バイポーラトランジスタは、第1の導電層を構成する基板と、第1の導電層上に配置されたn−hill層312と、n−hill層312を囲む素子分離酸化膜320に開口されたオープン領域と、オープン領域上に形成されるポリシリコン膜910と、ポリシリコン膜910から固相拡散されたエミッタ領域と、素子分離酸化膜320に形成されたダミーゲートポリシリコン706と、を有し、ダミーゲートポリシリコン706によってポリシリコン膜910からの固相拡散されるエミッタ領域の形状が制御される。

(もっと読む)

トランジスタ素子

【課題】単体構造のHBTデバイスと同等の信頼性を得る。

【解決手段】化合物半導体からなる、高電子移動度トランジスタ(HEMT)とヘテロバイポーラトランジスタ(HBT)とを、同一基板上に重ねてエピタキシャル成長した多層構造のトランジスタ素子において、エピ層として内在するインジウムガリウムリン層(InGaP)のバンドギャップエネルギを1.91eV以上にすることを特徴とする。

(もっと読む)

1 - 10 / 450

[ Back to top ]