国際特許分類[H01L21/8242]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | ダイナミックランダムアクセスメモリ構造 (2,471)

国際特許分類[H01L21/8242]に分類される特許

1,001 - 1,010 / 2,471

半導体装置

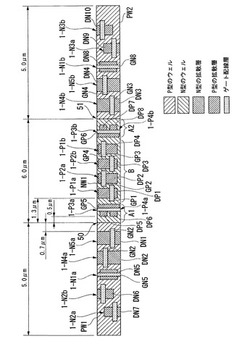

【課題】本発明は、このような事情に鑑みてなされたもので、高精度の閾値電圧制御が必要なMOSトランジスタに対し、従来に比較して閾値電圧の製造バラツキを低減させ、かつチップ面積を従来と同様とする半導体装置を提供する。

【解決手段】本発明の半導体装置は、n型のウェルNW1内に高精度の閾値電圧制御が必要なpMOSトランジスタ1−P1a、1−P1bを形成する際、ウェルNW1の外縁50あるいは51からの距離を大きくし、この空いた領域に、pMOSトランジスタ1−P1a、1−P1bのように高精度の閾値電圧制御が必要のないMOSトランジスタ1−P3a、1−P4a、1−P3b、1−P4bを形成することで、不純物濃度の均一な領域において、高い閾値電圧制御の必要なMOSトランジスタの閾値電圧の制御性を向上させ、かつ外縁50あるいは51近傍の不純物濃度が不均一な領域に高精度の閾値電圧制御の必要がないMOSトランジスタを形成することで、ウェル内を有効に用いている。

(もっと読む)

半導体装置

【課題】微細化が進んだ半導体装置の短チャネル効果を防ぎ、特性を向上させることができる半導体装置の提供を課題とする。

【解決手段】単結晶シリコン基板上に形成された酸化膜と、酸化膜上に形成された単結晶シリコン層と、単結晶シリコン層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極を有する半導体装置であって、単結晶シリコン層はチャネル形成領域、ソース領域、ドレイン領域を有し、チャネル形成領域には、ソース領域、ドレイン領域とは逆の導電型の不純物元素が添加され、チャネル形成領域の不純物元素が添加された領域は、上面から見て主軸がソース領域からドレイン領域にかけて伸びるフィッシュボーン形状を有し、フィッシュボーン形状は単結晶シリコン層の表面から底部にかけて形成され、チャネル形成領域の不純物元素が添加された領域は、空乏層を抑止する機能を有することを特徴としている半導体装置を提供する。

(もっと読む)

半導体装置

【課題】信頼性が高く、特性の改善された半導体装置を提供すること。

【解決手段】本発明の一態様に係る半導体装置1は、ワンチップに規則性を有するレイアウト領域と、規則性のないレイアウト領域を備える半導体装置であって、下層導電層11と、下層導電層11上に形成された層間絶縁膜と、その上に形成された上層配線層M1と、下層導電層11と上層配線層M1とを、実質的に最短距離で電気的に接続するように配設した接続プラグ10とを備える。そして、規則性を有するレイアウト領域における少なくとも一部の領域において、下層導電層11と上層配線層M1との電気的接続が、下層導電層11の直上から延在する直上位置、当該直上位置から離間したシフト位置に配設した少なくとも2つの接続プラグ10と、これらを電気的に接続するための中間接続層20により行われている。

(もっと読む)

集積回路デバイスのヒューズ構造

【課題】 集積回路デバイスのヒューズ構造を提供する。

【解決手段】 本発明のヒューズ構造は、半導体基板の一部の上に配置された金属含有導電性材料のストリップを含み、ストリップは、第1方向に沿って延伸し、均一な線幅を有する。誘電体層は、導電層を覆う。誘電体層内は、第1ビアと第2ビアを有し、第1インターコネクトと第2インターコネクトをそれぞれ含む。第1インターコネクトは、ストリップ上の第1位置と物理的且つ電気的に接触しており、第2インターコネクトは、ストリップ上の第2位置と物理的且つ電気的に接触している。導電ストリップ上の第1と第2位置は、シリコンを含まない。誘電体層の上方は、第1インターコネクトに電気的に接続された第1配線構造と、第2インターコネクトに電気的に接続された第2配線構造である。

(もっと読む)

導電物質を形成する方法、導電物質を選択的に形成する方法、プラチナを形成する方法、及び、導電構造を形成する方法

導電物質を選択的に形成する方法及び金属導電構造を形成する方法を開示する。下部に横たわる物質領域を露出するように有機物質をパターン化することができる。下部に横たわる物質の上に位置する有機物質の残留部分と反応することなく下部に横たわる物質と反応するプラチナ前駆ガス等の前駆ガスに、下部に横たわる物質を晒してもよい。前駆ガスを原子層蒸着処理に用いてもよく、その間、前駆ガスは導電構造を形成するように下部に横たわる物質と選択的に反応して有機物質とは反応しない。導電構造は、例えば、半導体デバイス製造の様々な段階においてパターニング用マスクとして用いることができる。 (もっと読む)

同軸のトランジスタ構造

【課題】 本発明は基板上での同軸トランジスタを開示する。

【解決手段】同軸構造のMOSFETであって、チップ或いは基板(Wafer Bonding)を積層し、軸心貫通孔により貫通し接続してより高い集積度及びラッチ効果のない同軸全対称のCMOSFETの集積回路を形成することができる。

(もっと読む)

半導体デバイスの製造方法

【課題】酸化剤の供給量や供給時間を増大させることなく酸化膜の被覆性やローディング効果を改善する。

【解決手段】少なくとも1枚の基板を処理室内に搬入する基板搬入工程と、前記基板を加熱しながら第1の反応物質と酸素原子を含む第2の反応物質とを前記処理室内に交互に供給して前記基板上に酸化膜を形成する酸化膜形成工程と、前記基板を前記処理室内から搬出する基板搬出工程と、備え、前記酸化膜形成工程では、基板温度が前記第1の反応物質の自己分解温度以下であり、前記第2の反応物質に紫外領域の光を照射することを特徴とする半導体デバイスの製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタを形成する工程において、キャパシタ孔が開孔しないことに起因した不良の問題がなく、また、梁の消失に起因した隣接する下部電極同士の接触の問題がない半導体装置の製造方法を提供する。

【解決手段】キャパシタを形成工程は、犠牲層間絶縁膜24a,bに長溝を形成する工程と、前記長溝にカーボン膜81を埋め込む工程と、前記カーボン膜81にキャパシタ孔を形成する工程と、前記キャパシタ孔内に下部電極51を形成する工程と、前記カーボン膜と犠牲層間絶縁膜を除去する工程と、を有する。

(もっと読む)

半導体装置

【課題】隣接するゲート電極間がショートすることを防止して、半導体装置の製造歩留まりを向上させる。

【解決手段】メモリセル領域に溝型ゲート電極構造のMOS型トランジスタ、周辺回路領域にはプレーナー型ゲート電極構造又は溝型ゲート電極構造のMOS型トランジスタが形成されるDRAMにおいて、ダミートランジスタ及び電界効果型トランジスタを第2の方向21に配列して、ダミートランジスタは第2の方向21に関して少なくとも一方の端に配置し、ダミートランジスタのゲート電極の埋設部36が電界効果トランジスタのゲート電極の埋設部36よりも第2方向21の幅が短い。

(もっと読む)

半導体装置

【課題】メモリ回路において、トランジスタの特性に依存することなく情報を保持できる時間のバラツキを是正する半導体装置を提供することである。

【解決手段】トランジスタの漏洩電流に対して別の電流経路を追加する。別の電流経路に流れる電流をトランジスタの漏洩電流に比べて大きくすることでトランジスタの特性に依存することなく情報を保持できる時間のバラツキを是正させる。構成としては、トランジスタに漏洩電流を流させないように容量と並列に素子を追加し、別の電流経路を設ける。

(もっと読む)

1,001 - 1,010 / 2,471

[ Back to top ]