国際特許分類[H01L23/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832)

国際特許分類[H01L23/00]の下位に属する分類

容器,封止 (4,129)

マウント,例.分離できない絶縁基板 (9,861)

容器の充填または補助部材,例.センタリング部材 (134)

封緘,例.封緘層,被覆 (7,021)

動作中の完全装置を支持する支持体,すなわち分離できる定着物 (458)

冷却,加熱,換気または温度補償用装置 (8,151)

動作中の固体本体からまたは固体本体へ電流を導く装置,例.リードまたは端子装置 (2,507)

動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814)

半導体装置に適用される標識,例.登録標識,テストパターン

放射,例.光,からの保護

他に分類されない半導体装置用構造的電気的装置 (109)

国際特許分類[H01L23/00]に分類される特許

31 - 40 / 648

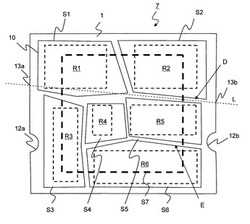

基板の遮へい構造及び電子機器

【課題】基板上の複数の遮へい対象領域を遮へいしつつ、外力が加わった際の基板及び基板に実装される集積回路及び電気部品を保護する。

【解決手段】基板の遮へい構造7は、一方の表面上に複数の遮へい対象領域R1〜R6が互いに離間して位置する基板1と、基板1の一方の表面4上に設けられ、各々が対応する遮へい対象領域R1〜R6を覆う複数の遮へい体S1〜S6と、を有している。複数の遮へい体S1〜S6は、複数の遮へい体S1〜S6の間を延びる溝部D,Eが基板1を直線状に横断することのないように位置している。

(もっと読む)

電子装置

【課題】ノイズ除去用のコンデンサの組み付けが容易な構造を備えた電子装置を提供する。

【解決手段】電子装置は、導電性のケース10と、一面21に回路チップ30が搭載されると共に他面22がケース10の内部に固定された基板20と、一端41が回路チップ30に電気的に接続されると共に他端42が外部に電気的に接続されるターミナル40と、を備えて構成されている。また、ターミナル40は、一部の表面に積層された誘電体層44と、この誘電体層44の上に積層された電極層45と、を有している。そして、ターミナル40、誘電体層44、および電極層45によりノイズ除去用のコンデンサ部43が構成され、コンデンサ部43の電極層45がケース10に電気的に接続されている。

(もっと読む)

高密度実装用基板、高密度実装用基板の判定方法と高密度実装用基板の実装方法

【課題】複数個の個片の高密度実装用基板と、捨て桟とからなる高密度実装用基板シートの場合、半導体チップや電子部品等を実装する良品部分と、これらの実装に適さない課題品部分とを区別するために、マーキング法が使われていたが、めっき層の周縁部の散乱光の影響を受けやすく、光学的な自動認識に課題があった。

【解決手段】複数個の個片の高密度実装用基板11と、捨て桟12とからなる高密度実装用基板シート13の場合、半導体チップや電子部品等を実装する良品部分と、これらの実装に適さない課題品部分とを区別するための識別マーク15を、配線19で形成し、この配線19の周縁部をレジスト17で覆うことで、周縁部からの散乱光32を低減し、光学的な自動認識性を高める。

(もっと読む)

印刷装置とその制御方法

【課題】印刷に関連する関連処理を円滑に実行できる印刷装置を提供する。

【解決手段】基材に対して液体の液滴を吐出して印刷を行う吐出ヘッドを有する。操作権限情報の入力を受け付けるとともに、入力された操作権限情報に対応して選択可能な印刷に関連する関連処理を表示し、選択された関連処理の実行の入力を受け付けたときに、関連処理の設定に関する操作情報を操作権限情報に応じた所定の操作手順に従って表示して、関連処理の設定の入力を受け付けるインターフェイス部IFを備える。

(もっと読む)

圧電デバイスとその製造方法

【課題】容器本体のキャビティに実装するICチップを有機樹脂で保護したことにより生じる出力周波数の変動を抑制し、当該ICチップの実装作業で生じる可能性がある当該ICチップの破損を回避する。

【解決手段】ICチップ8の容器本体1への実装面である一方の面に当該容器本体1の下部キャビティ3の底面に設けられた回路配線パターン7の端子パッドに接続するバンプ9を有するICチップ本体8aの面とは反対面に絶縁性の保護シート8bを貼付して固着した。

(もっと読む)

インターポーザ、インターポーザシート、インターポーザの判定方法とインターポーザの実装方法

【課題】複数個の個片のインターポーザと、捨て桟とからなるインターポーザシートの場合、半導体チップや電子部品等を実装する良品部分と、これらの実装に適さない課題品部分とを区別するために、マーキングペン法が使われていたが、金めっき層の周縁部の散乱光の影響を受けやすく、光学的な自動認識に課題があった。

【解決手段】複数個の個片のインターポーザ11と、捨て桟12とからなるインターポーザシート13の場合、半導体チップや電子部品等を実装する良品部分と、これらの実装に適さない課題品部分とを区別するための識別マーク15を、配線19で形成し、この配線19の周縁部をソルダーレジスト17で覆うことで、周縁部からの散乱光32を低減し、光学的な自動認識性を高める。

(もっと読む)

半導体パッケージ

【課題】配線の高密度化に対応させつつも、接続用パッドに認識マーク機能を持たせることができる半導体パッケージを提供する。

【解決手段】下側パッケージ1は、当該下側パッケージ1に搭載される半導体パッケージの接続端子と電気的に接続される複数の接続用パッド22と、その接続用パッド22のうち少なくとも2つの接続用パッド22Aの領域内に形成され、その接続用パッド22Aよりも小さい平面形状を有する認識マーク23と、を有している。

(もっと読む)

半導体モジュールの製造方法及び半導体モジュール

【課題】外装シールドを確実に接地するとともに、ダイシングブレード、外装シールドにかかる負担を抑えて半導体モジュールを製造する。

【解決手段】モジュール基板1と、モジュール基板1の上面に実装された複数個の電子部品2と、これらの電子部品2を含むモジュール基板1の上面を封止する封止樹脂層3と、封止樹脂層3の上面を覆う外装シールド4と、外装シールド4と一体に形成された接続部5とを備えている半導体モジュールA。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】位置合わせ精度の向上による接続信頼性の向上が可能な半導体装置を提供する。

【解決手段】半導体素子と、半導体素子に形成されている接続電極と、半導体素子に形成されているアライメントマークとを備え、アライメントマークの少なくとも1つ以上が磁性体からなる半導体装置を構成する。

(もっと読む)

磁気メモリチップを有する半導体装置の製造方法

【課題】アセンブリ段階において外部磁場から磁気メモリチップを保護する。

【解決手段】主面に磁気メモリ素子および複数のワイヤボンドパッドが形成された磁気メモリチップを準備する。シリコンより高透磁率を有する第1の磁気シールド板を磁気メモリチップの主面に搭載する。磁気メモリチップをリードフレームのダイパッド上に搭載しダイアタッチフィルムにより接着する。磁気メモリチップのワイヤボンドパッドとリードフレームのリードとをワイヤで電気的に接続する。磁気メモリチップ、磁気シールド板、ワイヤ及びリードの一部を樹脂により封止する。複数の磁気メモリチップを有するシリコンウェハを準備し、シリコンウェハの裏面を研削することによりシリコンウェハを所定の厚さまで薄くしてダイアタッチフィルムを張り付けた後にシリコンウェハをダイシングして各々がダイアタッチフィルムをその裏面に有する複数の磁気メモリチップを形成する。

(もっと読む)

31 - 40 / 648

[ Back to top ]