国際特許分類[H01L23/12]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | マウント,例.分離できない絶縁基板 (9,861)

国際特許分類[H01L23/12]の下位に属する分類

形状に特徴のあるもの (436)

材料またはその電気特性に特徴のあるもの (925)

国際特許分類[H01L23/12]に分類される特許

21 - 30 / 8,500

配線基板

【課題】半導体集積回路素子に対して十分な電源供給を行なって半導体集積回路素子を良好に作動させることが可能な配線基板を提供すること。

【解決手段】上面側のビルドアップ配線層3における電源プレーン3Pの中に形成された接地用のビアランド3Lおよびこれに接続されたビア6は、接地用の半導体素子接続パッド7Gの各列における一部のパッドにのみ対応するにように間引かれて形成されているとともに、電源用の半導体素子接続パッド7Pの各列から電源用のスルーホール5Pへの導電路が電源プレーン3Pにおける前記間引かれた部分を通るようにして形成されているとともに、下面側のビルドアップ配線層3におけるビアランド3Lは、複数一組のビア6に対応する分が一つに繋がっている。

(もっと読む)

半導体装置、半導体素子、及び半導体装置の製造方法

【課題】はんだによる短絡不良を低減すること。

【解決手段】半導体素子10の一主面には複数の電極パッド11が、半導体素子10の外周に沿って矩形枠状に配列されている。各電極パッド11には、柱状の電極端子13が立設されている。電極端子13の基端部(金属端子部15の基端部16及びバリア層14)は電極パッド11に接続されている。電極端子13(金属端子部15)の先端部17は略半円柱状に形成されている。この略半円柱状の先端部17は、先端面の弧部分が半導体素子10の外側を向くように形成されている。配線基板20の接続パッド22は、配列方向と直交する方向、即ち半導体素子10の外周と直交する方向に沿って延びる矩形状に形成されている。電極端子13は接続パッド22にはんだ30により電気的に接続される。

(もっと読む)

配線基板の製造方法

【課題】半田バンプ上に半導体素子の電極を安定した状態で載せて半導体素子の電極と半導体素子接続パッドとを電気的に良好に接続することが可能な配線基板の製造方法を提供する。

【解決手段】絶縁基板に半導体素子接続パッド及びソルダーレジスト層5bを形成する工程と、前記半導体素子接続パッド上にソルダーレジスト層5bの上面より高い半田バンプB1を溶着する工程と、ソルダーレジスト層5b及び半田バンプB1上にソルダーレジスト層5bを弾性変形で凹ませつつ半田バンプB1を塑性変形で押潰す様に押圧ローラーRを転動させて半田バンプB1の頭頂部をソルダーレジスト層5bの上面より低い位置となるように平坦化する工程とを行なう。

(もっと読む)

半導体パッケージ

【課題】差動モード信号の反射とコモンモード信号の反射とを個別に制御する。

【解決手段】半導体パッケージ内の整合回路20において、第1および第2の信号端子2p,2nは、半導体チップ10に設けられた差動信号の入出力用の一対のパッド1p,1nとボンディングワイヤでそれぞれ接続され、互いに容量結合するように構成される。第3および第4の信号端子3p,3nは、差動信号伝送用の一対の線路12p,12nとそれぞれ接続され、互いに容量結合するように構成される。第1〜第4の補助端子2g1,2g2,3g1,3g2は、第1〜第4の信号端子2p,2n,3p,3nとそれぞれ容量結合するように構成されるとともに、各々が接地電位と直接またはインダクタを介して接続される。第1のインダクタ5pは、第1および第3の信号端子2p,3p間に設けられる。第2のインダクタ5nは、第2および第4の信号端子2n,3n間に設けられる。

(もっと読む)

半導体モジュール

【課題】本明細書では、基板基材が熱によって劣化することを抑制することができる構造の半導体モジュールを開示する。

【解決手段】半導体モジュール2は、基板基材4内にIGBT10、ダイオード20、プリント配線30〜44、及び、断熱部50が配置されて形成されている。IGBT10とダイオード20は、基板基材4内に並べて配置されている。プリント配線30は、IGBT10及びダイオード20と接続されている。同様に、プリント配線34、36は、IGBT10と接続されている。また、プリント配線38は、ダイオード20と接続されている。プリント配線30〜44の一部は、基板基材4の表面に露出している。断熱部50は、IGBT10と基板基材4との間、ダイオード20と基板基材4との間、及び、プリント配線30、34、36、38と基板基材4との間に配置されている。

(もっと読む)

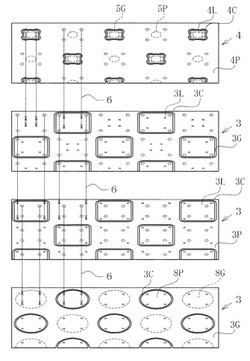

多数個取り配線基板、配線基板および電子装置

【課題】 多数個取り配線基板を分割する際にリードピン同士が接触することによってリードピンが変形することを低減すること。

【解決手段】 多数個取り配線基板10は、複数の配線基板領域1aを含んでおり、複数の配線基板領域1aの境界に設けられた分割溝2を有している母基板1と、複数の配線基板領域1aのそれぞれにおいて母基板1の表面に設けられた導体層3と、導体層3に接合されたリードピン4とを備えており、分割溝2の内面2aの延長線2bとリードピン4とが交わらないことを特徴とする。このような構成であることから、分割溝2の内面2aの対向する部分同士が接して多数個取り配線基板10が撓むことを抑制するので、隣接する配線基板領域1aに設けられたリードピン4同士が接触することが抑制され、配線基板11のリードピン4が変形することを低減できる。

(もっと読む)

電子装置及びその製造方法

【課題】Fan−out型のWLPにおいて、金属バンプの接合を確実に行う。

【解決手段】電子装置1は、回路基板2上にパッケージ部品5が金属バンプ4を介して実装されている。パッケージ部品5は、半導体チップ11を樹脂21で覆うと共に、再配線層31によって半導体チップ11の領域の外側に金属バンプ4を配置することが可能になっている。樹脂21内には、銅製の柱25が複数配置されており、各柱25の下方に金属バンプ4が1つずつ配置されている。パッケージ部品5を回路基板2に実装するときは、パッケージ部品5の上方から超音波を印加すると、柱25によって超音波が損失なく伝播させられ、金属バンプ4を溶融させる。

(もっと読む)

表面実装可能な集積回路のパッケージ化機構

【課題】表面実装可能な集積回路のパッケージ化機構を提供する。

【解決手段】集積回路(IC)パッケージが開示される。ICパッケージは、上部層、中間層、及び底部層を有する基板と、基板の上部層に埋め込まれたミリメートル波アンテナのアレイと、基板の底部層に実装されたモノリシック・マイクロ波集積回路(MMIC)とを含む。1つの実施形態において、プリント回路基板(PCB)への表面実装のための第2のレベルの相互接続が基板の底部層に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】導電箔とその保護膜が形成された絶縁基材に対して平行に半導体チップを固着し、熱膨張による応力を起因とした半導体装置の損傷の防止を図る。

【解決手段】絶縁基材11の表面上に導電箔12が配置され、導電箔12を覆って、その一部を露出する複数の第1の開口部17A、及び複数の第2の開口部17Bを有する保護膜17が配置されている。各第1の開口部17Aで露出する導電箔12の表面上に導電突起体14が配置される。表面に複数のパッド電極12を有した半導体チップ20は、その裏面が複数の導電突起体14と対向するように、ダイボンドペースト15を介して保護膜17上に固着される。各第2の開口部17Bで露出する導電箔12は、それぞれボンディングワイヤを介してパッド電極21と接続される。絶縁基材11の表面上の半導体チップ20等は、封止材16に覆われて封止される。

(もっと読む)

半導体パッケージ及びこれを含む半導体パッケージモジュール

【課題】工程コストが低減するとともに、製造工程が簡素化された半導体パッケージ及びこれを含む半導体パッケージモジュールを提供する。

【解決手段】本発明の半導体パッケージ100は、ボンディングパッド120を有する半導体チップ110と、ボンディングパッド120に電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターン141と、ショート(short)型再配線パターン141と同一層上で多数個に分離形成されたオープン(open)型再配線パターンAとを含む再配線層140と、オープン(open)型再配線パターンAそれぞれに形成された信号連結用接続端子1D、2Dとを有する第1基板150と、を含む。

(もっと読む)

21 - 30 / 8,500

[ Back to top ]