国際特許分類[H01L23/52]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814)

国際特許分類[H01L23/52]の下位に属する分類

半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851)

内部の相互接続を含むもの,例.クロスアンダ構造

絶縁基板の上または中に形成される複数の半導体チップ間の相互接続構造 (17)

国際特許分類[H01L23/52]に分類される特許

1 - 10 / 4,946

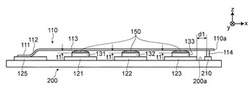

半導体装置の製造方法、半導体装置及び半導体装置の製造用治具

【課題】長尺接続子により直線上に配列された複数の半導体チップを半田付けにより共通接続する場合において、長尺接続子の撓みを防止して当該長尺接続子と各半導体チップとの間隔を適正な間隔に保持する。

【解決手段】長尺接続子110の接続板部113を当該長尺接続子110の先端部の側に位置する半導体チップ133よりもさらに先方にまで延長することによって形成された延長部150の下面側に突起部114を有する長尺接続子110と、リードフレーム120を載置するリードフレーム載置面200aに長尺接続子110の突起部114を当接させるための突起当接部210を有する台座200とを用いて、長尺接続子110の突起部114を台座200の突起当接部210に当接させるようにリードフレーム120を台座200に載置した状態で半導体チップ131〜133の各上面と長尺接続子110の接続板部113の下面とを半田付けする。

(もっと読む)

半導体ウエハーの接合方法および半導体装置の製造方法

【課題】積層された半導体ウエハーが備える接続部間の電気的な接続を安定的に行い得るとともに、効率よく複数の半導体素子を製造し得る半導体ウエハーの接合方法および信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体ウエハーの接合方法では、半導体ウエハー210と半導体ウエハー220との間に、フラックス活性を有する硬化剤と、熱硬化性樹脂とを含む接合層60を介在させて、半導体ウエハー210、220が積層された半導体ウエハー積層体230を得た後に、半導体ウエハー積層体230を、加熱しつつ、その厚さ方向に加圧することにより、半田バンプ224を溶融・固化するとともに、前記熱硬化性樹脂を硬化して、半導体ウエハー210と半導体ウエハー220とが固着することにより、接続部(半田バンプの固化物)225で、接続部212と接続部222とが電気的に接続された半導体ウエハー接合体240を得る。

(もっと読む)

電子装置及びその製造方法

【課題】信頼性の高い電子装置及びその製造方法を提供する。

【解決手段】複数のチップ12a,12bと、複数のチップを埋め込む樹脂層10と、互いに隣接するチップ同士を電気的に接続する配線26と、配線により電気的に接続されたチップに係合し、樹脂層より熱膨張率が低く、配線により電気的に接続されたチップ同士を固定する固定部材18とを有している。

(もっと読む)

電気装置の製造方法、半導体基板の製造方法、電気装置用形成基板、及び電子機器

【課題】静電破壊を防止して歩留まり良く製造できる電気装置の製造方法、半導体基板の製造方法、電気装置用形成基板、及び電子機器を提供する。

【解決手段】支持体上に、樹脂材料からなる基材を複数積層することで第1基板を形成する工程と、素子基板から前記支持体を剥離する工程と、素子基板との間で機能素子を挟持するように第2基板を貼り付ける工程と、を有する電気装置の製造方法に関する。素子基板の形成工程においては、複数の基材間のいずれかに挟持するように電極層を配置するとともに、電極層よりも上層であって複数の前記基材間のいずれかに挟持する或いは基板本体の表面に配置するように機能素子を駆動するための半導体素子を設ける。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体パッケージ内における半導体素子の位置ずれを抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、凸部23が形成されたパッケージ基板11、導電性の接着剤25、およびパッケージ基板11上に実装された半導体素子14、を具備する。パッケージ基板11は、少なくとも2箇所に凸部23が形成された基板である。導電性の接着剤25は、凸部23を含むパッケージ基板11上に形成される。パッケージ基板11上に実装される半導体素子14は、各凸部23に係合する複数のバイアホール24を有している。さらに、半導体素子14は、少なくとも2箇所のバイアホール24が、各凸部23に接着剤25を介して係合するようにパッケージ基板11上に実装される。

(もっと読む)

半導体パッケージ

【課題】支持板の一面側に固着された厚さの異なる複数の半導体素子の各電極端子に形成されたバンプの露出面間隙を通して引き回すことのできる配線パターンの高密度化を図る。

【解決手段】厚さの異なる複数の半導体素子14a,14bが、その電極端子16の端子面が同一面となるように、支持板10の一面側に樹脂層12によって固着されている半導体パッケージであって、樹脂層12は支持板10の一面側全面に設けられ、半導体素子14a,14bは端子面の反対面が樹脂層12に固着され、半導体素子14a,14bの端子面および側面の少なくとも一部ならびに樹脂層12の表面全面を被覆する絶縁層20が設けられ、半導体素子14a,14bの端子面に形成された先細り状のバンプ18が絶縁層20を貫通して形成され、絶縁層20の表面に露出している先細り状のバンプ18の先端面が配線パターン22に接続される。

(もっと読む)

半導体装置

【課題】配線基板上にメモリチップとマイコンチップとを搭載してシステムを構成するシステム・イン・パッケージ(SIP)型半導体装置の小型化、高速化を推進する。

【解決手段】配線基板10の上面にマイコンチップ20とメモリチップ30を搭載する際、メモリチップ30の第1チップ辺31a(データ系電極パッド33Dが配置された辺)に沿って配置された配線基板10の第2導電パッド15が、平面視において、マイコンチップ20の第3チップ辺21cの延長線と第4チップ辺21dの延長線との間の領域に位置するようにメモリチップ30を配置することで、マイコンチップ20のデータ系電極パッド23Dとメモリチップ30のデータ系電極パッド33Dとを接続するデータ系配線16Dの長さを最短化する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】電気的特性がより向上した半導体装置の製造方法を提供すること。

【解決手段】封止金型5内で、第一の半導体素子1が搭載された第一の金属基板2の一部に、第二の半導体素子3が搭載された第二の金属基板4の一部を、接合材料6を介して押圧しつつ、封止金型5内にモールド樹脂10を充填させる充填工程と、モールド樹脂10を硬化するとともに、接合材料6を用いて第一の金属基板2の一部20と第二の金属基板4の一部41の間を接合する硬化接合工程とを備えた、半導体装置の製造方法である。

(もっと読む)

半導体装置、半導体装置の製造方法、固体撮像装置及び電子機器

【課題】 ビア形成時のエッチングによる基板や配線への影響を抑制しつつ積層された半導体ウェハの回路どうしを接続する。

【解決手段】 半導体装置の製造方法は、第1基板と第1基板の一面と接するように形成された第1絶縁層を有する第1の半導体ウェハと、第2基板と第2基板の一面と接するように形成された第2絶縁層を有する第2の半導体ウェハを接合する工程と、第1基板の他面に第3絶縁層を形成する工程と、第3絶縁層、第1基板、及び第1絶縁層を貫通し第2絶縁層に形成された第2の配線上に第2絶縁層が残るようにエッチングを行い第1接続孔を形成する工程と、第1接続孔に絶縁膜を形成する工程と、第2の配線上の第2絶縁層及び絶縁膜のエッチングを行い第2接続孔を形成し第2の配線を露出させる工程と、第1及び第2接続孔の内部に形成され第2の配線と接続する第1のビアを形成する工程とを備え、第1基板の他面に形成された第1接続孔の径は第3絶縁層に形成された前記第1接続孔の径より大きい。

(もっと読む)

積層チップパッケージおよびその製造方法

【課題】正常に動作しない半導体チップを含んでいても、正常に動作しない半導体チップを含んでいない場合と同等の機能を有するパッケージを容易に実現できるようにする。

【解決手段】積層チップパッケージ1Mは、本体2と配線3を備えている。本体2は、積層された複数の階層部分を含む主要部分2Mと、主要部分2Mの上面と下面に配置された複数の端子を有している。配線3は複数の端子に接続された複数のライン(ワイヤW)を含んでいる。複数のラインは、複数の共通ラインと複数の階層依存ラインを含んでいる。各階層部分は、複数の共通ラインに接続された複数の共通電極と、複数の階層依存ラインに接続され、階層部分内の半導体チップに接触しない複数の非接触電極と、複数の階層依存ラインのうち、その階層部分が利用する階層依存ラインにのみ選択的に接続された選択的接続電極を含んでいる。階層依存ラインは、共通ラインに比べて最大の幅が大きい。

(もっと読む)

1 - 10 / 4,946

[ Back to top ]