国際特許分類[H01L23/532]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814) | 半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851) | 材料に特徴のあるもの (313)

国際特許分類[H01L23/532]に分類される特許

1 - 10 / 313

半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

Cu層形成方法及び半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

リフロー法及び半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置およびその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

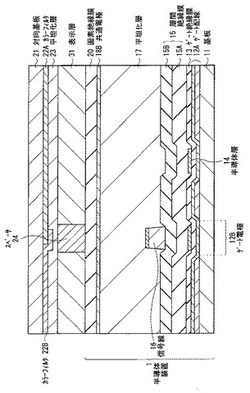

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

配線及び半導体装置

【課題】実施形態は、多層グラフェンの配線及び多層グラフェン配線を有する半導体装置を提供することを目的とする。

【解決手段】実施形態にかかる配線は、基板と、基板上に設けられた金属膜と、記金属膜上に設けられた金属部と、金属部に形成されたグラフェン配線とを有し、前記グラフェン配線は、前記金属膜と電気的に接続し、金属膜と金属部は、異なる金属または合金であることを特徴とする。

(もっと読む)

絶縁膜形成方法及び絶縁膜形成装置

【課題】信号遅延の抑制と絶縁性の向上との両立が可能な絶縁膜形成方法及び絶縁膜形成装置を提供する。

【解決手段】

シリコン貫通電極用の貫通孔が形成されたシリコン基板を備える基板Sに絶縁膜を形成するに際し、抵抗加熱ヒータ33Hによって加熱された基板Sを収容する反応室31Sに、酸素ガス及びキャリアガスであるアルゴンガスと混合されたZr(BH4)4を供給する。そして、Zr(BH4)4を上記基板S上で熱酸化することによって、基板Sの表面及び上記貫通孔の内側面にジルコニウム、ホウ素、及び酸素を含む絶縁膜の一つであるZrBO膜を形成する。

(もっと読む)

半導体製造装置及び半導体製造方法

【課題】エッチング工程を行う際の窒化膜のエッチング選択比を向上できる半導体製造装置及び方法が提供される。

【解決手段】本発明による半導体製造装置は工程チャンバーの外部で供給されるジフルオロメタンCH2F2、窒素N2、及び酸素O2ガスからプラズマを発生させ、発生されたプラズマを工程チャンバー内へ供給する。プラズマが工程チャンバーへ供給される途中に三フッ化窒素NF3が供給される。このような装置構造及びソースガスを利用してシリコン窒化膜をエッチングすると、他の種類の膜に対するシリコン窒化膜のエッチング選択比を大きく増加させることができる。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

1 - 10 / 313

[ Back to top ]